18-Bit Pipeline DSP Slice IP

The 18-bit Pipeline DSP slice IP Core provides the best utilization of device resources like memory, I/O, processor and clock.

Overview

The 18-bit Pipeline DSP slice IP Core provides the best utilization of device resources like memory, I/O, processor and clock. It is based on pipelining technique which uses instruction level parallelism within a single processor.

Key features

- Timing resolution: 80ps

- Operating frequency range: 160MHz – 700 MHz

- Lock time: 11 cycles

- Generates user configurable precise phase shifts from 00 to 3600 with a resolution of 10

- Delays multiple periodic or aperiodic signals independent of voltage and temperature.

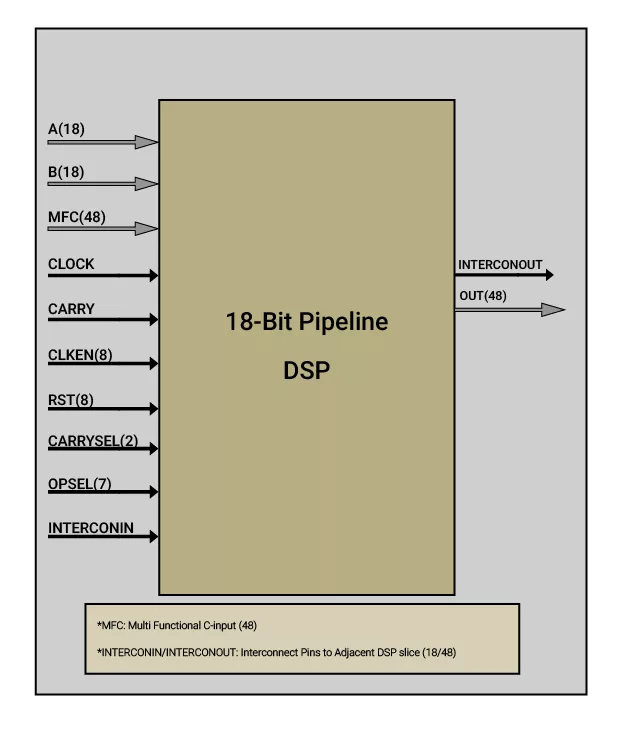

Block Diagram

Benefits

- It support many independent functions, including multiplier, multiplier accumulator (MAC), multiplier-adder, higher bit adder, 3-input adder, barrel shifter, wide bus multiplexers, magnitude comparator, and counter. It also supports connecting multiple DSP slices IP Core to form wide math functions, DSP filters, and complex arithmetic. The architectural highlights of 18-bit Pipeline DSP slice IP core are as follows:

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Arithmetic Units IP core

ML-KEM explained: Quantum-safe Key Exchange for secure embedded Hardware

Accelerating RTL Design with Agentic AI: A Multi-Agent LLM-Driven Approach

LTE Single Carrier DFT: Faster Circuits with Reduced FPGA LUT/Register Usage

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Computing dons new suits as required

Frequently asked questions about Arithmetic Unit IP cores

What is 18-Bit Pipeline DSP Slice IP?

18-Bit Pipeline DSP Slice IP is a Arithmetic Units IP core from Faststream Technologies listed on Semi IP Hub.

How should engineers evaluate this Arithmetic Units?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Arithmetic Units IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.