PCI Express Phy IP

Welcome to the ultimate PCI Express Phy IP hub! Explore our vast directory of PCI Express Phy IP

All offers in

PCI Express Phy IP

Filter

Compare

296

PCI Express Phy IP

from

24

vendors

(1

-

10)

-

PCIe Gen4.0 PHY IP

- Best-in-class Power / Performance / Area competitiveness

- Compliant to PCIe 4.0 Base specification

- Supports lane configurations according to the user’s demands

- Supports data rates of 2.5GT/s, 5.0GT/s, 8.0GT/s and 16GT/s

-

PCIe Gen5/6 PHY IP

- Best-in-class Power / Performance / Area competitiveness

- Compliant to PCIe 5.0/6.x Base specification

- Supports lane configurations according to the customer’s demands

- Supports data rates of 2.5GT/s, 5.0GT/s, 8.0GT/s, 16GT/s, 32GT/s and 64GT/s (PAM4)

-

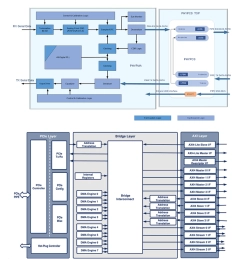

PCIe PHY and controller solution

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

PCIe 6.0 PHY, TSMC N3A x4 1.2V, North/South (vertical) poly orientation for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Supports the latest features of PCIe 6.x and CXL 3.x specifications

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Delivers more power efficiency across channels with unique DSP algorithms

- Enables near zero link downtime with patent-pending diagnostic features

-

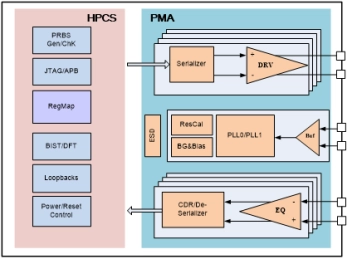

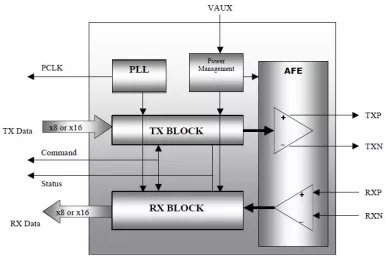

PCI Express PIPE PHY Transceiver

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

-

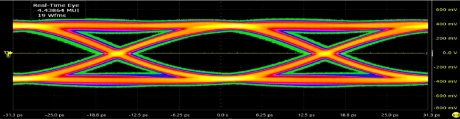

PCIe Gen 6 Phy

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- PCIe Gen 6 Phy IPPCIe Gen 6 Phy IPComprehensive real-time diagnostic, monitor, and test features

-

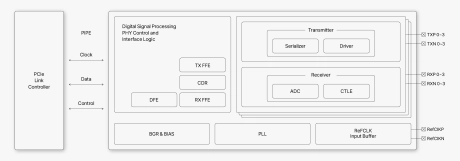

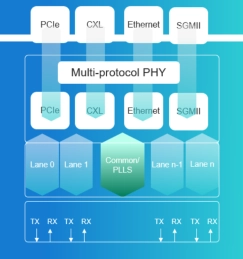

PCIe 6.0 / CXL 3.0 PHY & Controller

- Innosilicon’s PCIe 6.0 and CXL 3.0 IP solutions combine high-performance controllers and PHYs, fully compliant with PCIe 6.0, CXL 3.0, and PIPE specifications

- These solutions deliver exceptional performance, low latency, power efficiency, and unparalleled flexibility, making them ideal for enterprise computing, data centers, cloud servers, AI and machine learning, storage expansion, and high-speed interconnect applications

-

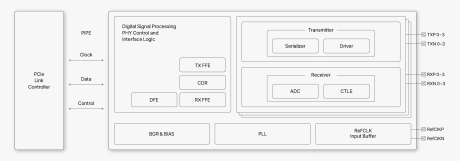

PCIe 5.0/4.0/3.0 PHY & Controller

- Innosilicon’s PCIe 5.0 IP solutions combine high-performance controllers and PHYs, fully compliant with PCIe 5.0/4.0/3.0, and PIPE specifications

- These solutions deliver exceptional performance, low latency, power efficiency, and unparalleled flexibility, making them ideal for enterprise computing, storage networks, automotive, and I/O connectivity applications

-

PCIe GEN6 PHY IP

- The PCIe GEN6 PHY IP achieves data rates up to 64GT/s per lane with PAM4 signaling thereby delivering reliable performance for high-speed data transfer.

- It supports advanced applications, including AI/ML, High-Performance Computing, and next-generation storage solutions.

-

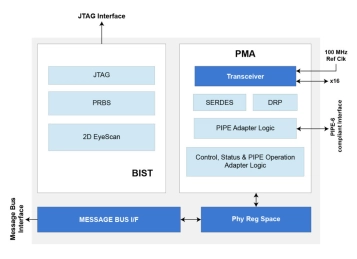

PCIE 6.0/5.0/4.0/3.0/2.0

- Support PCI Expression Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- Configurable differential voltage swing

- Embedded low jitter LC PLL with fixed bandwidth and output frequency

- PLL Frequency Lock detection