PCIe PHY and controller solution

Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance.

Overview

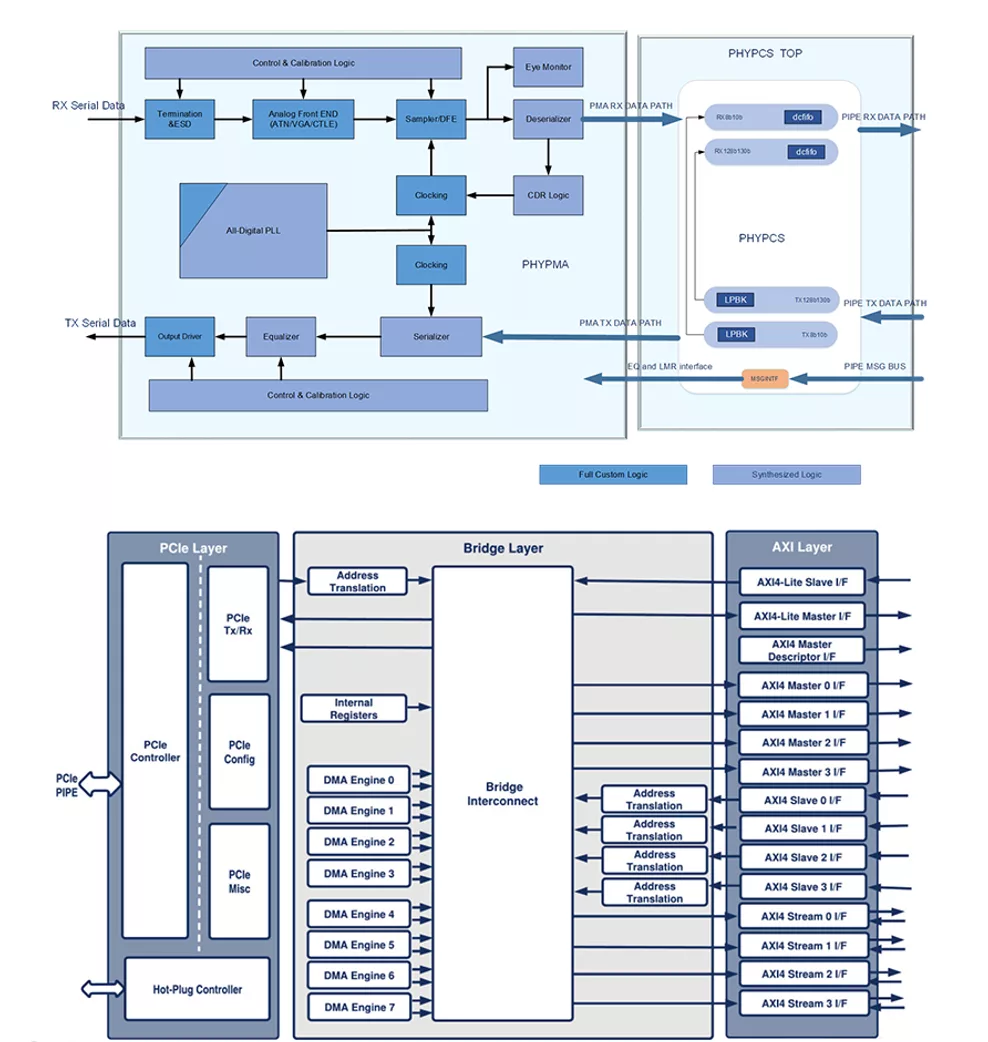

Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios. Besides the high performance of the PHY with its high line rate, low latency operation is a key feature of the PCIe PHY. The PHY supports data rate from 2.5Gbps to 16Gbps to cover PCIe Gen4.0/3.0/2.0/1.0. The common high-speed LC-PLL clock generation can supply clock up to 8+ lanes depending on jitter requirement, so that flexible macro configuration of e.g. 1x,2x,4x,8x are possible.

Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

Key features

Controller Features:

- x1, x2, x4, x8, x16 PCI Express Core

- Supports link rate of 2.5, 5.0, 8.0 and 16.0 per lane

- 8-bit, 16-bit, 32-bit, 64-bit and 128-bit PIPE interface

- PHY Interface for PCI Express (PIPE), Revision 4.4.1 compliant

- PCI Express® Base Specification Revision 4.0 v1.0 compliant

- 4 KByte maximum payload size

- 1 Virtual Channel (VC)

- Lane reversal support

- Integrated Clock Domain Crossing (CDC) to support user-selected frequency for the Bridge

- Optional AXI4-Lite Slave interface for Bridge Configuration

- Optional AXI4-Lite Master interface for External Registers Configuration

PHY Features:

- Metal stack 1P9M, and above

- Constant latency of 1.5-word clocks

- Maximum 35db Insertion loss support

- Flexible macro configurations

- Maximum x8 support with a single CMU

- Self-adaption of all major calibration and adaptive processes supported for robust performance

- Software control and override of all auto-adaption processes supported

- Support for both common reference clock and Separate Reference Clock without SSC (SRNS)

- SSC supported

- Max. of +/-300ppm frequency offset for separate reference clock mode

- On-die Eye Monitor for RX performance and TX-to-RX loopback performance

- DIR mode for link EQ training supported (PIPE)

- RX eye monitor implemented

- Fully compliant with PCIE Express Base 4.0, PCI Express Base 3.1/2.1/1.1 electrical specifications

- PIPE Revision 4.4.1 compliant

- Different loopback modes: near-end serial, far-end parallel

Block Diagram

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCIe PHY and controller solution?

PCIe PHY and controller solution is a PCI Express IP core from Brite Semiconductor listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.