PCI Express PIPE PHY Transceiver

SMS5000 is a fully integrated CMOS transceiver that handles the full Physical Layer PCI Express protocol and signaling.

Overview

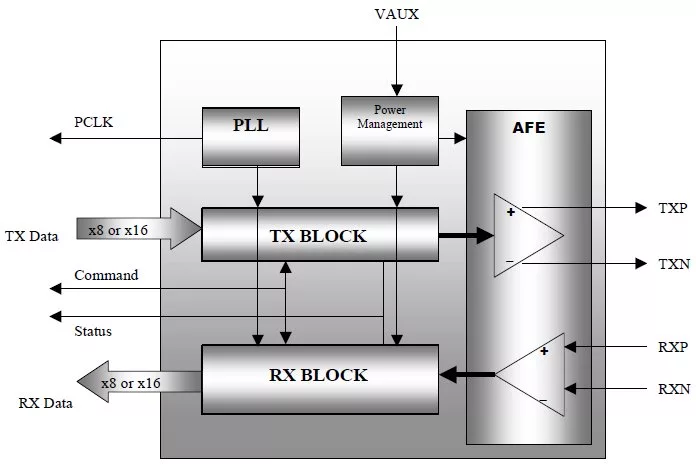

SMS5000 is a fully integrated CMOS transceiver that handles the full Physical Layer PCI Express protocol and signaling. It contains all necessary AFE (Analog Front End), Clock synthesis, Clock Recovery, Serializer, De-serializer, Comma detect for 8B/10B encoded data and frame alignment functionalities. Digital controller interface is realized with a 8-bit parallel operation (Optional 16-bit Interface) that allows use of 250 MHz reference Clock. The transceiver includes Receiver Detection, Beacon Generation, Beacon Detection and Signal Detect capability compliant with PCI Express Specification requirements and provides Short Circuit Protection to ground for outputs. SMS5000 also includes calibrated Transmitter and Receiver Termination Resistors compliant with the requirements of the PCI Express Base 1.0a Specification.

SMS5000 does not require any external Loop filter capacitor(s) for clock Synthesis PLL or Clock recovery circuitry making it immune to PCB related noise typically encountered, and provides a completely integrated solution.

Key features

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

- Supports direct disparity control for use in transmitting compliance pattern

- 8b/10b encode/decode and error indication

- Receiver detection

- De-emphasis at Transmit

- Electrical Idle Generation & Detection

- Lane Polarity Inversion Support

- Loop-back Support

- Spread Spectrum Clock Support

- Embedded Bit Error Rate Testing Through PBRS generation and detection

- Short Circuit Protection

- Scrambling Disable Feature

- Beacon transmission and detection

- Direct Disparity Control Support for use in transmitting compliance pattern

- Full low cost, low power CMOS Implementation

- Modular architecture supports 1,2,4,8,16 Lane applications

- Optimized, Proprietary architecture yields very small silicon area

- Hot Swap, Hot Plug Support

Block Diagram

What’s Included?

- GDS2

- Full behavioral model

- test vectors

- test bench for integration testing

- verification environment

- characterization and testing documents

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- LAN : Fast (100Base-Tx), Gigabit (fiber or copper) & 10 Gigabit ETHERNET

- WAN : SONET ( OC-3, OC-12, OC-48 ), Broadband Cable Modem, DSL

- SAN/Connectivity : Fibre-Channel, Infiniband, USB2.0, IEEE 1394, SERDES, Backplane, PCI Express PIPE, and Chip to Chip connectivity.

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is PCI Express PIPE PHY Transceiver?

PCI Express PIPE PHY Transceiver is a Single-Protocol PHY IP core from Soft Mixed Signal Corp. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.