1394b PHY IP Core

The 1394b PHY core includes all functionality needed to meet the AS5643 protocol, and provides a IP solution for the PHY layer of…

Overview

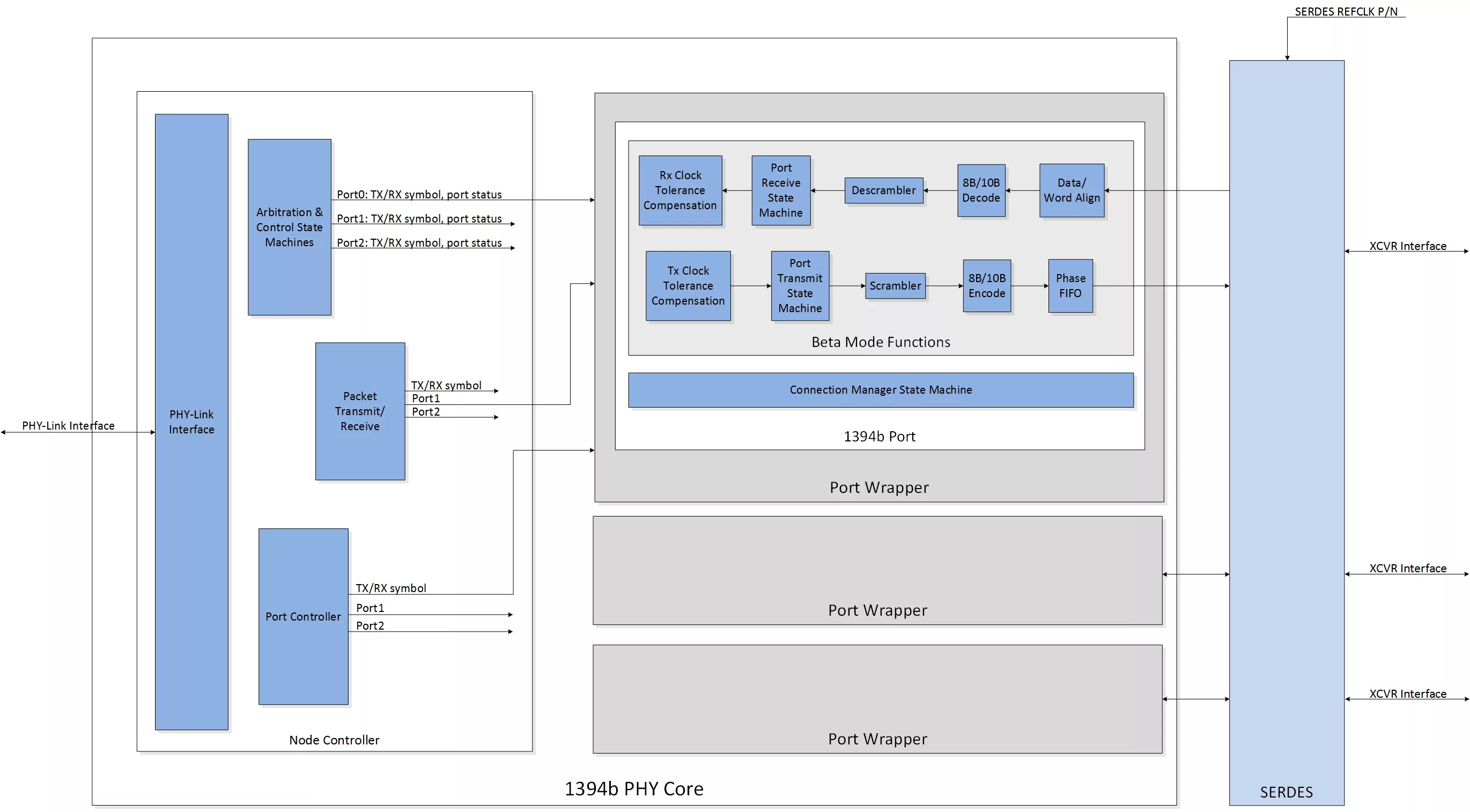

The 1394b PHY core includes all functionality needed to meet the AS5643 protocol, and provides a complete IP solution for the PHY layer of the 1394b. The 1394b core includes all functionality needed to meet the 1394b and AS5643 support specification, including: comma alignment, 8b/10b encode/decode, primitive decode, scrambling, port state machine, connection manager, arbitration controller, elastic FIFO, and phase FIFO.

At the physical layer, the core of 1394b is built for connecting to FPGA/ASIC embedded SERDES, discrete SERDES parts, or general-purpose IO with AS5643 performance protocol. The Link Layer interface of 1394b PHY IP’s core provides the industry standard PHY-Link interface. This PHY-Link interface connects directly to New Wave Design’s Link Layer IP cores, discrete Link Layer integrated circuits, or to custom logic developed by the end user.

This core is targeted towards Mil1394 aerospace and defense applications and has been used on a wide range of FPGA devices at varying operating rates. The core comes with test-benches and example code, making design integration a straightforward task.

Key features

- AS5643 compliant interface

- Supports S100/S200/S400 data rates

- Configurable number of ports per PHY instantiation

- Configurable number of PHYs in a single FPGA

- Standard PHY-Link interface Mil1394 targeted PHY layer implementation

Block Diagram

Benefits

- Increase interface port density while lowering size and power

- Additional diagnostics and programmable operation features

- Leverage proven technology for standard interface implementation

Applications

- Vehicle System – Remote Node

- Vehicle System – Vehicle Management Computer Avionic Mission Systems

What’s Included?

- Core is delivered in netlist format including constraint files

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Firewire IP core

Skillfully Emulating a System on Chip

Will Thunderbolt kill SuperSpeed USB?

Avoiding design errors in 1394-based external storage systems

SuperSpeed USB 3.0: Ubiquitous Interconnect for Next Generation Consumer Applications

How to cascade external storage with Serial ATA

Frequently asked questions about FireWire IP cores

What is 1394b PHY IP Core?

1394b PHY IP Core is a Firewire IP core from New Wave Design & Verification listed on Semi IP Hub.

How should engineers evaluate this Firewire?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Firewire IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.