IEEE 1394a - 2000 Link Layer Controller

The Link core is a functional block available for insertion into a customer's ASIC design, which supports the IEEE 1394a - 2000 D…

Overview

The Link core is a functional block available for insertion into a customer's ASIC design, which supports the IEEE 1394a - 2000 Draft specifications for a high - speed serial bus. The SI16FWA20 Link core is implemented using VHDL synthesizable code to provide portability across Silicon Interfaces Gate Array and Cell - Based ASIC technologies.

SI16FWA20, 1394a - 2000 Link Layer Controller Core provides data packet delivery service for Asynchronous and Isochronous (real - time) data transmission. It performs arbitration request, packet generation and checking as well as data and acknowledgement transmission. Packet Generation includes setting up of Packet Header, Address, Data CRC, Packet Channel, Destination Address and Transaction Code. Silicon Interfaces® Link Layer Controller core also provides complete support for bus Cycle Master and cycle control operation. SI16FWA20 is designed to support 100, 200 and 400 Mbps transmission, when used with the appropriate external Physical Layer device. This depends upon the speed provided with a 2 bit, 4 bit or 8 bit interface, which does not require special high - speed buffers. Besides, this version supports generation of LPS (Link Power Status) signal, based on the current mode in which the device operates (Differentiated or Undifferentiated).

SI16FWA20 highly integrated single - chip core is Silicon Interfaces® Intellectual Property and represents the company's proven Link Layer design experience as well as expertise in the field of complex designs. The complete modular design of SI16FWA20 core facilitates easy customization in order to include value added distinguished features.

Product Specifications :

- Modes : Asynchronous, Asynchronous Stream and Isochronous Stream

- Core : Fully synthesizable Register Transfer Level (RTL) VHDL

- Test Environment : Reusable Verilog with abundant scenarios

- Targeted FPGA : Xilinx Spartan-6 / Virtex-6

- Clock Frequency : 50 MHz

Key features

- Fully compliant with IEEE 1394a - 2000 Standard.

- PHY - Link I/F conforms to the specifications described in the section 5A of IEEE 1394a - 2000 standard.

- Half - duplex mode of operation.

- Programmable bus rates of 100/200/400 Mbps.

- Supports following Packet types : Asynchronous, Asynchronous Stream, Isochronous Stream and Cycle Start.

- Supports, in all, 13 Packet Formats - 10 Asynchronous, 1 Asynchronous Stream, 1 Isochronous and 1 Cycle Start.

- Maximum payload sizes of 2K bytes (Asynchronous) and 4K bytes (Isochronous).

- Cycle Master cable.

- 4K bytes of Transmit and Receive FIFO.

- Supports both Differentiated and Undifferentiated modes.

- Disabling of PHY - Link I/F through LPS output pin.

- Restoring of PHY - Link I/F through LinkOn_digital input pin.

- Reception of Isochronous Stream Packets regardless of Isochronous period.

- Supports transmission of concatenated packets at assorted modes and speeds.

- Selective programming of arbitration enhancements through Acceleration Control Request.

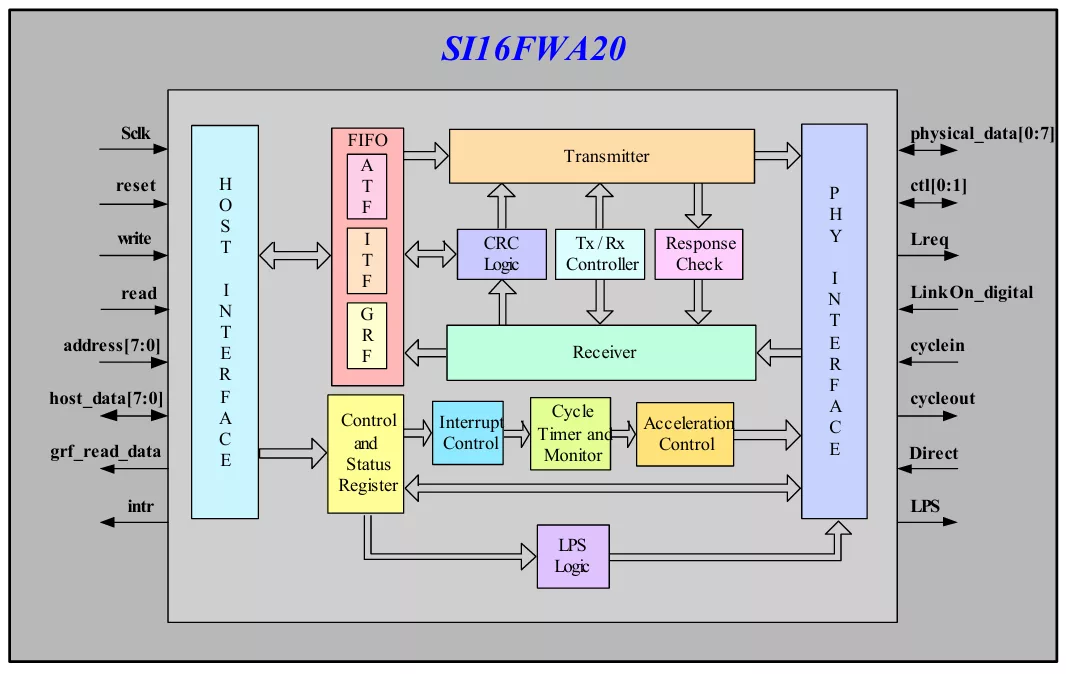

Block Diagram

What’s Included?

- Fully synthesizable Register Transfer Level (RTL) VHDL core.

- Test Bench Environment: Verilog

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Firewire IP core

Skillfully Emulating a System on Chip

Will Thunderbolt kill SuperSpeed USB?

Avoiding design errors in 1394-based external storage systems

SuperSpeed USB 3.0: Ubiquitous Interconnect for Next Generation Consumer Applications

How to cascade external storage with Serial ATA

Frequently asked questions about FireWire IP cores

What is IEEE 1394a - 2000 Link Layer Controller?

IEEE 1394a - 2000 Link Layer Controller is a Firewire IP core from Silicon Cores - a Div. of Silicon Interfaces listed on Semi IP Hub.

How should engineers evaluate this Firewire?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Firewire IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.