Clock Generator PLL IP for TSMC

Welcome to the ultimate

Clock Generator PLL IP

for

TSMC

hub! Explore our vast directory of

Clock Generator PLL IP

for

TSMC

All offers in

Clock Generator PLL IP

for

TSMC

Filter

Compare

211

Clock Generator PLL IP

for

TSMC

from

9

vendors

(1

-

10)

-

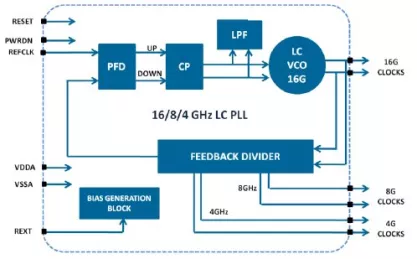

High Speed 16GHz PLL

- Type II ,3rd order low jitter PLL

- Auto calibration for process and temperature (USP)

- Programmable frequency using CSR registers

- 8/10/16GHz quadrature clocks

- Operating temperature -40 to 125

-

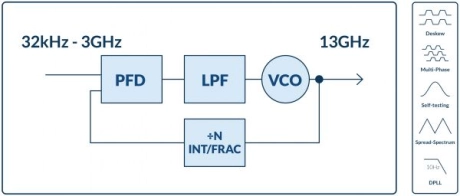

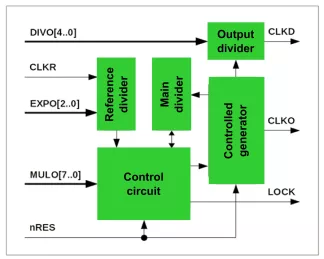

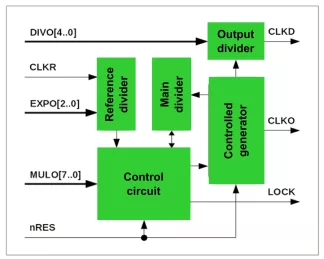

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

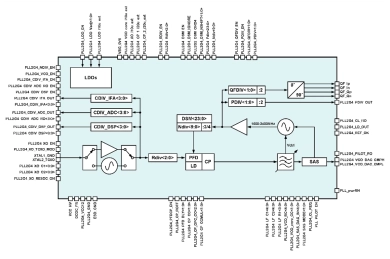

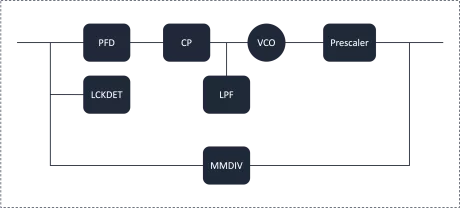

100 to 1200MHz phase-locked loop

- TSMC CMOS 55 nm

- Output frequency range from 100 MHz to 1200 MHz

- Fully integrated VCO

-

50-800 MHz phase-locked loop frequency synthesizer

- TSMC CMOS 55 nm

- Output frequency range from 50 MHz to 800 MHz

- Fully integrated VCO

- Reference frequency range from 4 MHz to 20 MHz

-

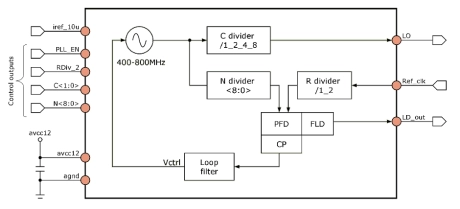

14GHz Integer-N High-Speed PLL

- Type II hybrid Integer-N LC-PLL

- Quadrature clocks at 14GHz and 7GHz

- Fast locking

-

Fully Digital Glitch Free PLL TSMC 16FFC 16 nm - 300-3000 MHz

- Ideal as a clock generator for digital design

- Excellent frequency jitter performance

- Ultra-low area fully digital PLL design

- Patented glitch free frequency adjustment

-

Fully Digital Glitch Free PLL TSMC HPC+28nm - 200-2000 MHz

- Ideal as a clock generator for digital design

- Excellent frequency jitter performance

- Ultra-low area fully digital PLL design

-

-

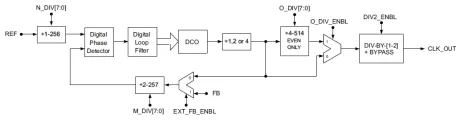

Low Jitter Digital PLL – 1.25G/2.5G/5G

- Type II, 3rd order low jitter PLL

- Auto calibration for process and temperature

- Programmable frequency using CSR registers

- 1.25GHz/2.5GHz/5GHz quadrature clocks

- Operating temperature -40 to 125