Ultra Ethernet's Design Principles and Architectural Innovations

By Torsten Hoefler 1,2, Karen Schramm 3, Eric Spada 3, Keith Underwood 4, Cedell Alexander 3, Bob Alverson 4, Paul Bottorff 4, Adrian Caulfield 5, Mark Handley 5, Cathy Huang 6, Costin Raiciu 3, Abdul Kabbani 7, Eugene Opsasnick 3, Rong Pan 8, Adee Ran 9, Rip Sohan 8

1 ETH Zurich, Switzerland

2 Microsoft, USA

3 Broadcom,USA

4 Hewlett Packard Enterprise, USA

5 OpenAI,USA

6 Intel,USA

7 Microsoft, USA

8 AMD,USA

9 Cisco, USA

Abstract

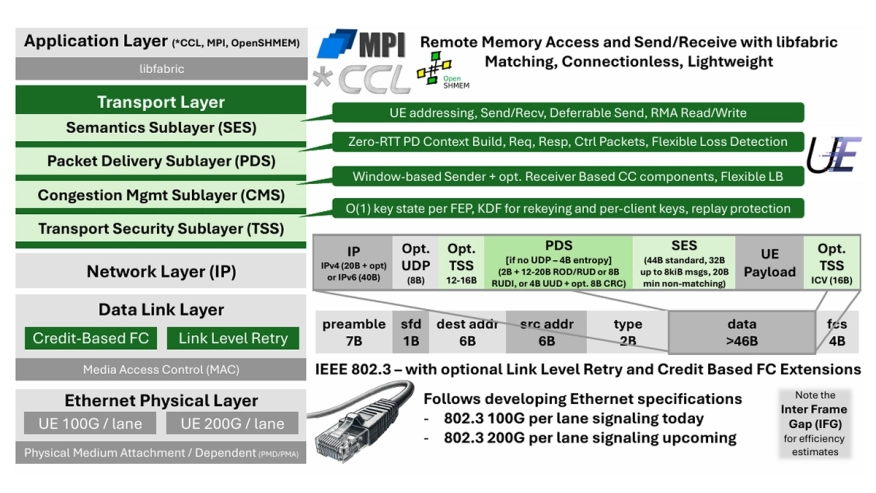

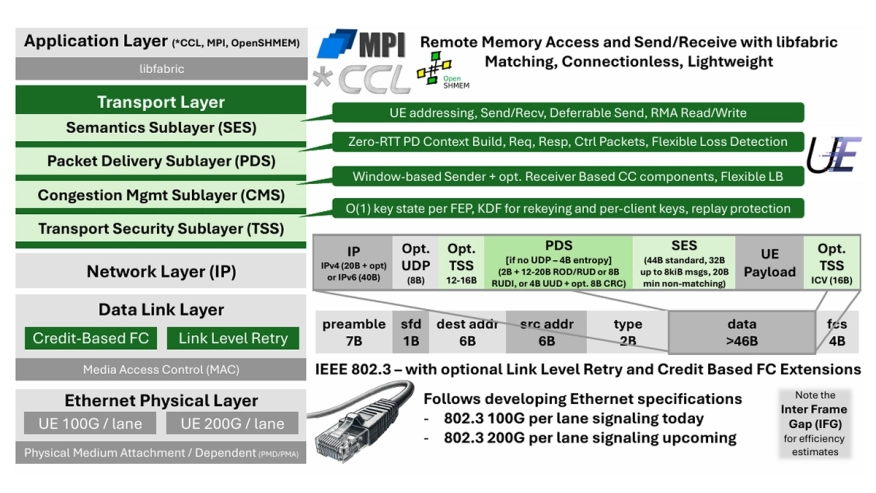

The recently released Ultra Ethernet (UE) 1.0 specification defines a transformative High-Performance Ethernet standard for future Artificial Intelligence (AI) and High-Performance Computing (HPC) systems. This paper, written by the specification's authors, provides a high-level overview of UE's design, offering crucial motivations and scientific context to understand its innovations. While UE introduces advancements across the entire Ethernet stack, its standout contribution is the novel Ultra Ethernet Transport (UET), a potentially fully hardware-accelerated protocol engineered for reliable, fast, and efficient communication in extreme-scale systems. Unlike InfiniBand, the last major standardization effort in high-performance networking over two decades ago, UE leverages the expansive Ethernet ecosystem and the 1,000x gains in computational efficiency per moved bit to deliver a new era of high-performance networking.

The recently released Ultra Ethernet (UE) 1.0 specification defines a transformative High-Performance Ethernet standard for future Artificial Intelligence (AI) and High-Performance Computing (HPC) systems. This paper, written by the specification's authors, provides a high-level overview of UE's design, offering crucial motivations and scientific context to understand its innovations. While UE introduces advancements across the entire Ethernet stack, its standout contribution is the novel Ultra Ethernet Transport (UET), a potentially fully hardware-accelerated protocol engineered for reliable, fast, and efficient communication in extreme-scale systems. Unlike InfiniBand, the last major standardization effort in high-performance networking over two decades ago, UE leverages the expansive Ethernet ecosystem and the 1,000x gains in computational efficiency per moved bit to deliver a new era of high-performance networking.

To read the full article, click here

Related Semiconductor IP

- Multi-channel Ultra Ethernet TSS Transform Engine

- Verification IP for Ultra Ethernet (UEC)

- Ultra Ethernet Verification IP

- 100G MAC/PCS Ultra Ethernet

- Complete 1.6T Ultra Ethernet IP Solution

Related Articles

- Convey UHD 4K Video over 1Gbit Ethernet with the intoPIX JPEG 2000 "Ultra Low Latency" compression profile

- How Ultra Ethernet And UALink Enable High-Performance, Scalable AI Networks

- Opto-electronics -> Architectural synthesis provides flexibilty in optical network design

- 10-Gbit Ethernet revenues to reach $3.6 billion by '04, says Dataquest

Latest Articles

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks

- Assertain: Automated Security Assertion Generation Using Large Language Models

- VolTune: A Fine-Grained Runtime Voltage Control Architecture for FPGA Systems

- A Lightweight High-Throughput Collective-Capable NoC for Large-Scale ML Accelerators

- Quantifying Uncertainty in FMEDA Safety Metrics: An Error Propagation Approach for Enhanced ASIC Verification