Runtime Energy Monitoring for RISC-V Soft-Cores

By Alberto Scionti 1, Paolo Savio 1, Francesco Lubrano 1, Olivier Terzo 1, Marco Ferretti 2, Florin Apopei 2, Juri Bellucci 3, Ennio Spano 4, Luca Carriere 4

1 Links Foundation, Turin, Italy

2 Teseo SpA– EES CLEMESSY, Druento, Italy

3 Morfo Design srl, Sesto Fiorentino, Italy

4 GEAvio srl, Rivalta di Torino, Italy

Abstract

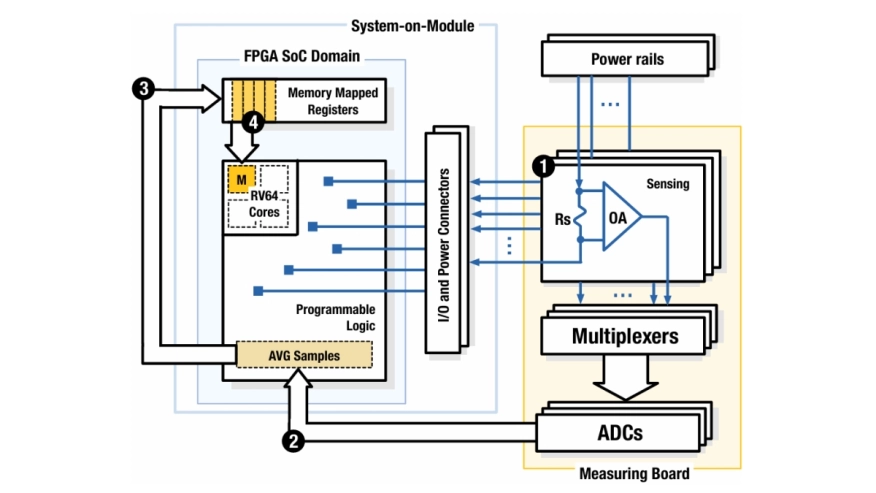

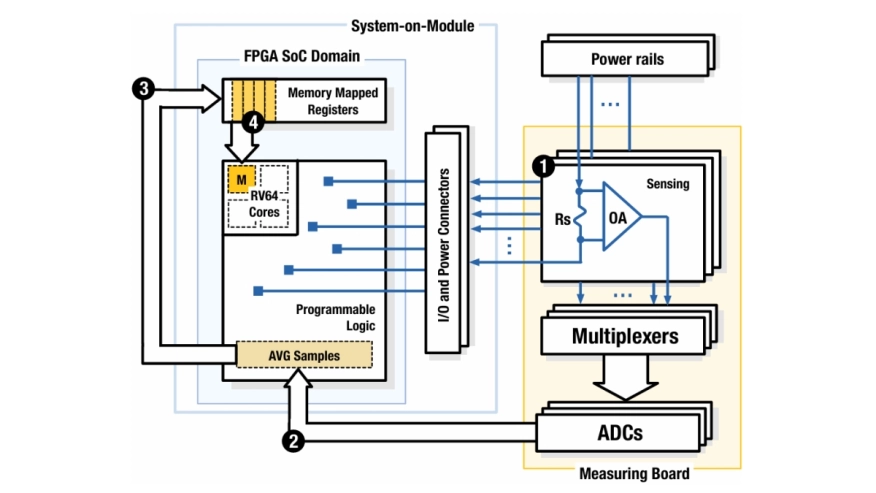

Energy efficiency is one of the major concern in designing advanced computing infrastructures. From single nodes to large-scale systems (data centers), monitoring the energy consumption of the computing system when applications run is a critical task. Designers and application developers often rely on software tools and detailed architectural models to extract meaningful information and determine the system energy consumption. However, when a design space exploration is required, designers may incur in continuous tuning of the models to match with the system under evaluation. To overcome such limitations, we propose a holistic approach to monitor energy consumption at runtime without the need of running complex (micro-)architectural models. Our approach is based on a measurement board coupled with a FPGA-based System-on-Module. The measuring board captures currents and voltages (up to tens measuring points) driving the FPGA and exposes such values through a specific memory region. A running service reads and computes energy consumption statistics without consuming extra resources on the FPGA device. Our approach is also scalable to monitoring of multi-nodes infrastructures (clusters). We aim to leverage this framework to perform experiments in the context of an aeronautical design application; specifically, we will look at optimizing performance and energy consumption of a shallow artificial neural network on RISC-V based soft-cores.

Energy efficiency is one of the major concern in designing advanced computing infrastructures. From single nodes to large-scale systems (data centers), monitoring the energy consumption of the computing system when applications run is a critical task. Designers and application developers often rely on software tools and detailed architectural models to extract meaningful information and determine the system energy consumption. However, when a design space exploration is required, designers may incur in continuous tuning of the models to match with the system under evaluation. To overcome such limitations, we propose a holistic approach to monitor energy consumption at runtime without the need of running complex (micro-)architectural models. Our approach is based on a measurement board coupled with a FPGA-based System-on-Module. The measuring board captures currents and voltages (up to tens measuring points) driving the FPGA and exposes such values through a specific memory region. A running service reads and computes energy consumption statistics without consuming extra resources on the FPGA device. Our approach is also scalable to monitoring of multi-nodes infrastructures (clusters). We aim to leverage this framework to perform experiments in the context of an aeronautical design application; specifically, we will look at optimizing performance and energy consumption of a shallow artificial neural network on RISC-V based soft-cores.

To read the full article, click here

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related Articles

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Interstellar: Fully Partitioned and Efficient Security Monitoring Hardware Near a Processor Core for Protecting Systems against Attacks on Privileged Software

- Why RISC-V is a viable option for safety-critical applications

- Optimizing Energy Efficiency in Subthreshold RISC-V Cores

Latest Articles

- Microarchitectural Co-Optimization for Sustained Throughput of RISC-V Multi-Lane Chaining Vector Processors

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation