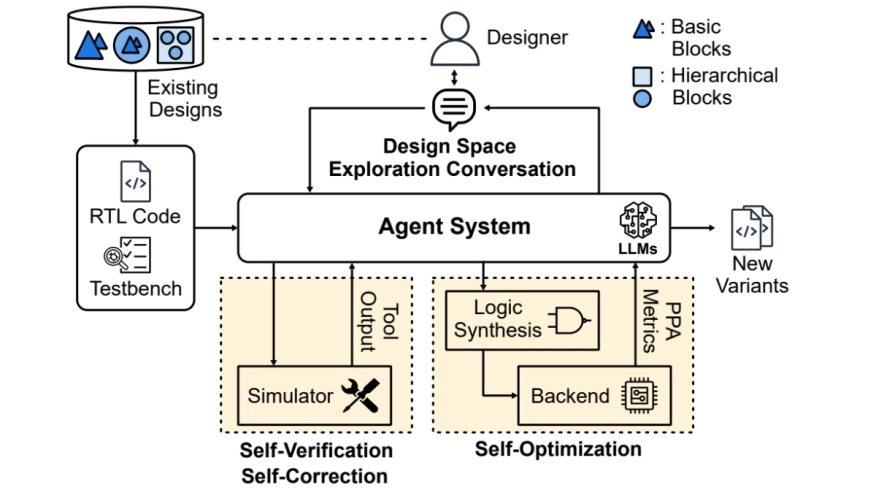

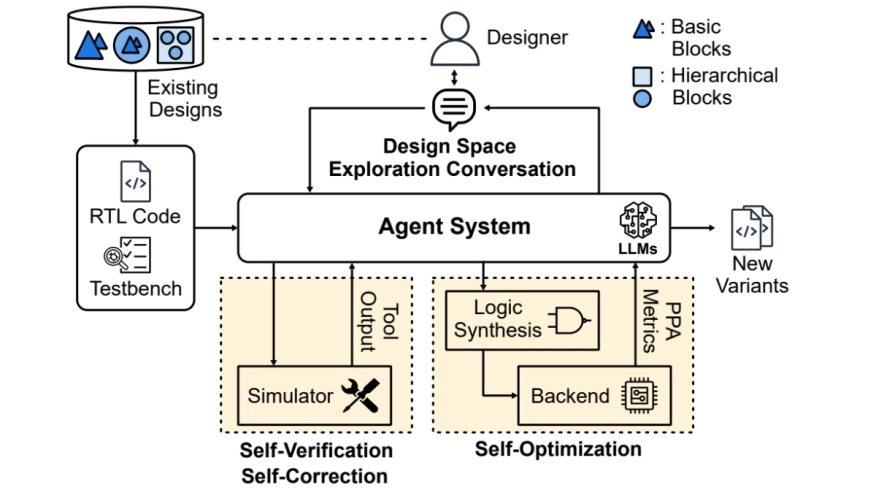

CRADLE: Conversational RTL Design Space Exploration with LLM-based Multi-Agent Systems

By Lukas Krupp, Maximilian Schoffel, Elias Biehl, and Norbert Wehn ¨

RPTU University of Kaiserslautern-Landau, Kaiserslautern, Germany

Abstract

This paper presents CRADLE, a conversational framework for design space exploration of RTL designs using LLM-based multi-agent systems. Unlike existing rigid approaches, CRADLE enables user-guided flows with internal selfverification, correction, and optimization. We demonstrate the framework with a generator-critic agent system targeting FPGA resource minimization using state-of-the-art LLMs. Experimental results on the RTLLM benchmark show that CRADLE achieves significant reductions in resource usage with averages of 48% and 40% in LUTs and FFs across all benchmark designs.

This paper presents CRADLE, a conversational framework for design space exploration of RTL designs using LLM-based multi-agent systems. Unlike existing rigid approaches, CRADLE enables user-guided flows with internal selfverification, correction, and optimization. We demonstrate the framework with a generator-critic agent system targeting FPGA resource minimization using state-of-the-art LLMs. Experimental results on the RTLLM benchmark show that CRADLE achieves significant reductions in resource usage with averages of 48% and 40% in LUTs and FFs across all benchmark designs.

Index Terms—LLM, Agents, Design Space Exploration, RTL

To read the full article, click here

Related Semiconductor IP

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

- ReRAM NVM in DB HiTek 130nm BCD

- UFS 5.0 Host Controller IP

Related Articles

- Veri-Sure: A Contract-Aware Multi-Agent Framework with Temporal Tracing and Formal Verification for Correct RTL Code Generation

- Simultaneous Exploration of Power, Physical Design and Architectural Performance Dimensions of the SoC Design Space using SEAS

- Simultaneous Exploration of Power, Physical Design and Architectural Performance Dimensions of the SoC Design Space using SEAS

- Configure, Confirm, Ship: Build Secure Processor-Based Systems with Faster Time-to-Market

Latest Articles

- VolTune: A Fine-Grained Runtime Voltage Control Architecture for FPGA Systems

- A Lightweight High-Throughput Collective-Capable NoC for Large-Scale ML Accelerators

- Quantifying Uncertainty in FMEDA Safety Metrics: An Error Propagation Approach for Enhanced ASIC Verification

- SoK: From Silicon to Netlist and Beyond Two Decades of Hardware Reverse Engineering Research

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks