Next Generation Wireless IP for the Internet of Things

By Narasimhan Venkatesh, Redpine Signals, Inc.

Abstract :

Most embedded systems today use some form of wireless connectivity. Specifically, the Internet of Things would not be possible without wireless interfaces. There are many considerations in the integration of wireless connectivity into the core system-on-chip around which systems are built. This paper provides a perspective on the integration of wireless connectivity subsystems within the system-on-chip (SoC).

INTRODUCTION

Wireless connectivity is a key component, or can even be considered the key component, of the Internet of Things. Embedded systems in the Medical, Building Automation, Smart Grid, Transportation, Industrial, and Logistics markets are more often built with wireless connectivity than without. There are multiple wireless standards in use today – each designed for a different purpose or application, but several of them are in use in the IoT. These include Zigbee, Bluetooth EDR and LE, and 802.11 WLAN. The Internet of Things, specifically Machine to Machine communications (M2M), is currently heterogeneous. It is not necessarily true that devices and equipment be designed afresh to be M2M capable. Rather, automation systems are bringing in a host of legacy equipment, sensors, and other devices into the M2M network concept. Increasingly, this involves centralizing the intelligence in automation in a server while keeping devices relatively simple. The key here is to enable devices to communicate to the server through any means possible – in particular choosing a method that is easily available and cost-effective. We can certainly make out a case for universally using Ethernet for wired needs and IEEE 802.11 WLAN for wireless, but we would then be ignoring the simplicity of RS-232 and its large established base, the applicability of Bluetooth LE to miniature battery operated devices, Zigbee in areas with no centralized wireless infrastructure, and so on.

The established practice of driving down implementation costs of electronic systems through higher levels of integration continues to be valid for these systems. The core component of these embedded systems is the microcontroller unit – and in this paper we provide a perspective on the integration of wireless connectivity subsystems within the system-on-chip (SoC).

WIRELESS IP COMPONENTS

Wireless networking is heavily standards-driven. Adherence to protocols is a critical requirement. All parts of a wireless subsystem are, therefore, designed to meet the requirements of the standards. However, different implementations can vary a lot in performance – the ability to transfer data at a given rate across a specific range at a specific energy cost.

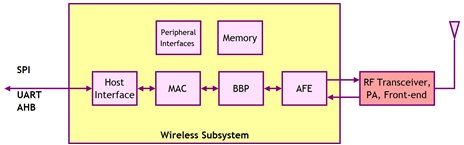

The components of the Wireless IP encompass hardware as well as software implementations. Figure 1 shows a generic hardware breakdown.

The RF subsystem is designed for the required frequency of operation, bandwidth, speed of response to received signals, spectral emission norms, and signal quality requirements. There are trade-offs involved in optimizing for performance versus power consumption. The analog front-end (AFE) is also designed similarly – the primary specifications being the bandwidth of operation and signal quality.

The all-digital baseband processor and MAC subsystems are usually built with a mix of hardware logic and firmware running on an embedded processor.

ADDRESSING KEY CHALLENGES

Apart from the usual best practices in IP integration, there are several specific areas that SoC integrators as well as IP designers must consider carefully for successful integration of a wireless interface into a system. We go through some of these below.

RF Interface

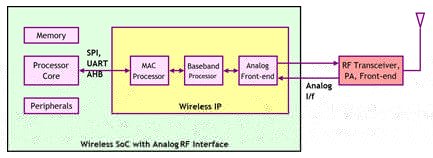

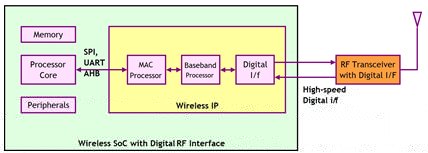

An A majority of wireless standards used in the Internet of Things are based on the license-free ISM bands. These RF frequencies of 900 MHz to 5.8 GHz require specialized RF devices to handle – at least according to the state of the art in technology today. The prevalent practice in the building of embedded systems at present is the use ofto use self-contained wireless modules that handle hardware as well as software functionality completely. The best case for integration is, of coursetherefore, to include all the hardware within the core MCU semiconductor device. The MAC layer processor and the baseband processor are digital subsystems that can be integrated into SoCs relatively easily. In the data transmit direction, the baseband processor output is converted to analog form before being modulated on to the required RF frequency. In the data receive direction, the down-converted output of the RF transceiver is transformed to digital form through an Analog-to-Digital converter before the baseband processor works on it. Although the analog and RF circuits are build commonly on CMOS today, there is still difficulty in migrating them across technology nodes. This is an obstacle to full integration. However, there are obstacles in the path here – the chief one being the difficulty of migrating RF and analog subsystems across technology nodes. As a middle practical solution, a preferred approach would be to integrate all the digital subsystems into the SoC. A key enabler of this approach is a digital interface between the baseband processor and the RF transceiver. There have been efforts in the past to standardize this interface, but the challenge is the very high bandwidth needed for data transfer here. For example, for 802.11n WLAN, a capacity of at least 1.6 Gbps would be required in each direction. With the analog front-end within the device, the interface between the baseband processor and the analog subsystem is a large parallel bus that is not practical as a chip level interface, especially while keeping devices small and inexpensive. A solution is to use specially defined high speed digital interfaces that optimize for pin count and clock rate on the interface.

POWER MANAGEMENT

Maximizing battery life is a major objective in most wireless systems. This is addressed in the SoC somewhat differently at its wireless subsystem block than in the rest of the chip. Here the accent is on low energy rather than low power. Wireless IP subsystems are usually optimized to offer receiver performance that maximizes the possible data rate for a given signal condition rather than to minimize instantaneous power consumption. Energy saving is then achieved with low granular switching on or off portions of the circuit. The integration of wireless IP into the SoC must provide for the required power modes. Typical wireless network protocol uses half-duplex communication with well defined operational profiles. The standards also provide for low power sleep or dormant modes devices may use during idle periods. Wireless devices can additionally exploit these facilities to reduce energy consumption. Wireless IP should allow low granular switching of portions of their circuit, and SoCs must provide for the use of these modes through hardware and firmware control. The system as a whole would then be able to exhibit lower average energy consumption.

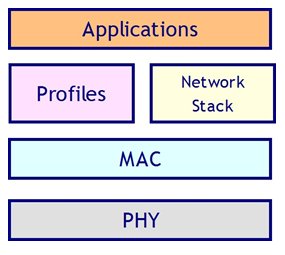

SOFTWARE INTEGRATION

Interoperable wireless connectivity is highly software intensive. Layers of protocol shroud the basic data transfer process. A broad view is presented in Figure 3. The self-contained module approach used in present systems ensures that the host MCU is kept relatively free of the burden of implementing protocol software or firmware. In some cases, particularly in WLAN, high throughput configurations often have part of the MAC layer and all of the Network layer run on the high performance host processor. For most IoT applications, however, it is advantageous to have the MCU software free of the networking stack details, leaving the processor fully available for the actual application. The Wireless IP would need to include a processor of its own to run the protocol functions. The communication between the host and the IP is usually therefore non-standard, and the IP would need to offer an easy to use interface with well-defined APIs that abstract the low level interface procedures. Software also plays a key role in ensuring interoperability and certification worthiness of the system. Integration of protocol software would therefore need to be free of dependencies and be relatively unaffected by applications or profiles built into the system. A highly abstracted interface with clean APIs would help ensure this.

CONVERGENCE OF MULTIPLE WIRELESS PROTOCOLS

Addressing the heterogeneous IoT market requires devices or systems at some points in the network that handle multiple wireless protocols. For example, an M2M gateway might offer wireless links using Zigbee, Bluetooth, WLAN and LTE. Wireless convergence within a device requires special design in the digital hardware as well as in the analog and RF. In addition, firmware specifically handling coexistence is essential. It is possible to have more than one wireless interface simultaneously active independently in real time – for example, BT 4.0 operating in the 2.4 GHz band and WLAN operating in the 5 GHz band. However, interfaces sharing the same band would need intelligent time sharing and other coexistence mechanisms.

COMPLIANCE TESTING AND MANUFACTURABILITY

A complete system would be expected to go through regulatory compliance in the geographic domains of interest. These tests use special modes for signal transmission to aid spectral measurements. The firmware in the wireless IP would need to provide for operation in these modes.

The wireless IP must also provide for configurability and data transfer needs for interoperability testing, enabling successful deployment in the field.

Wireless devices at manufacture time are usually subjected to performance tests and, if required, calibration. These procedures require special modes to be provided for in hardware and software. These must also flow through the integration process and be available at the system level.

Figure 1: A Generic Wireless Subsystem

Figure 2: Wireless IP Options

Figure 3: Generic Wireless Software Stack

Related Semiconductor IP

- 802.11i Wireless Security Cores

- 802.11 a b and g IEEE Standard - Wireless LAN

- LDPC Decoder for 5G NR and Wireless

- Multi-protocol wireless platform integrating Bluetooth Dual Mode, IEEE 802.15.4 (for Thread, Zigbee and Matter)

- Multi-protocol wireless plaform integrating 802.11ax (Wi-Fi 6), Bluetooth 5.4 Dual Mode, 802.15.4 (for Thread, Zigbee and Matter)

Related White Papers

- Low-Power wireless sensor networks for the Internet of Things

- Using sub-gigahertz wireless for long range Internet of Things connectivity

- Wireless communication standards for the Internet of Things

- Colibri, the codec for perfect quality and fast distribution of professional AV over IP

Latest White Papers

- Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity