The Benefits of a Multi-Protocol PMA

By Jeff Galloway, Chung-Chun (CC) Chen, Soumya Morgan — Silicon Creations

Introduction

At Silicon Creations, we have developed a power and area optimized, flexible and programmable PMA (Physical Medium Attachment) architecture that can be reliably ported to different process nodes and scaled across protocol generations as data rates increase. It is called the Multi-Protocol PMA, or MP-PMA for short. The architecture and programmability of the MP-PMA enables an SoC (System on Chip) developer to use the same PMA across a wide range of industry standard protocols, covering several different market applications. Our customers have deployed this MP-PMA in a wide range of process nodes supporting numerous protocols such as PCIe, DisplayPort, USB, and V-by-one. The next few sections go over the basic requirements of an MP-PMA and how the Silicon Creations’ MP-PMA meets these requirements.

PMA Definition

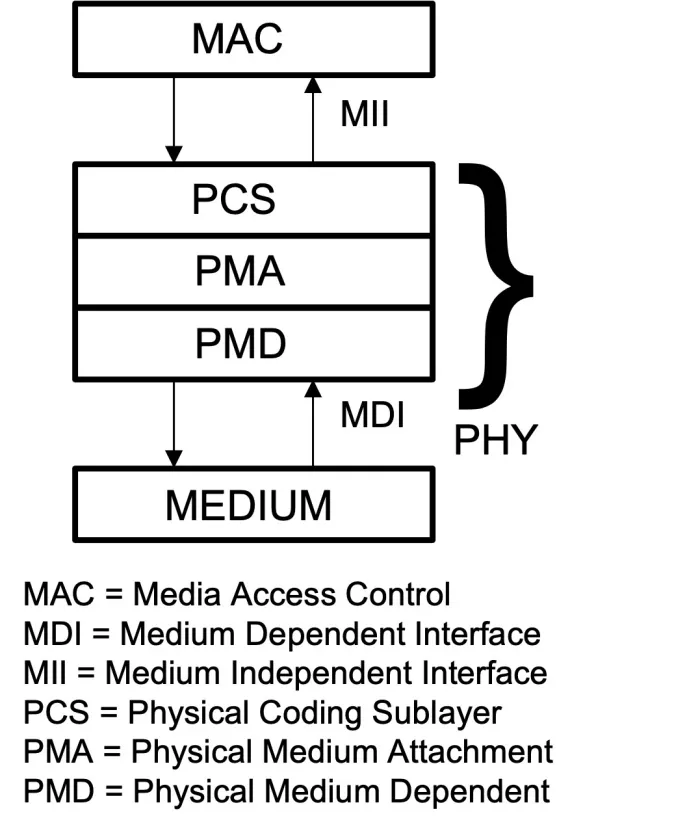

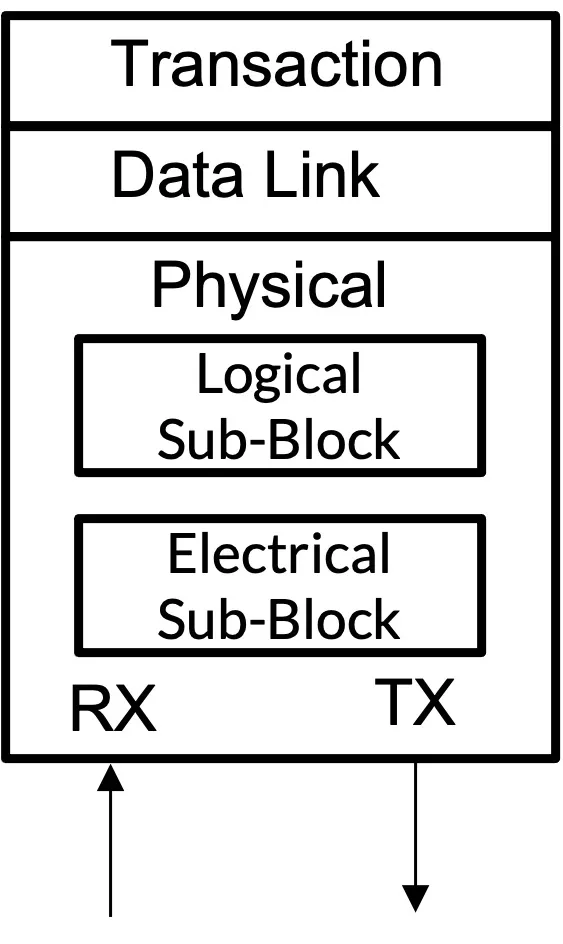

The PMA is a sub-layer in the IEEE 802.3 networking model that connects the physical medium dependent interface (MDI) to the Physical Coding sublayer (PCS). In PCIe and DisplayPort, this layer is called the Electrical Sub-block of the Physical layer. Some other protocols call this block the Physical Layer. At Silicon Creations, we use the term PMA for the IP that addresses this critical function.

Figure 1. Block diagram of IEEE 802.3 layers.

Figure 2. Block diagram of PCIe Layers

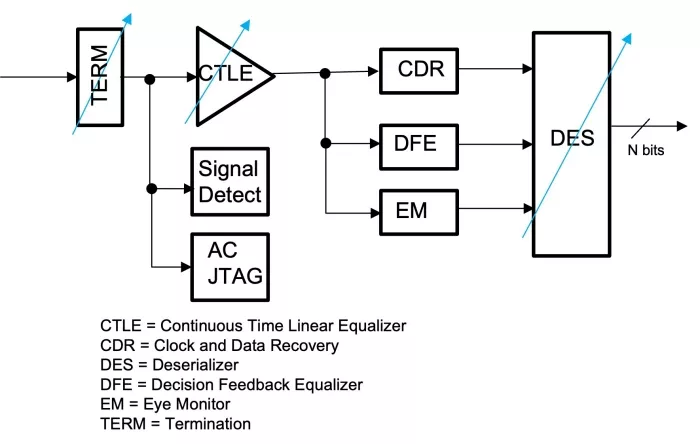

PMAs consist of a receiver (RX) and a transmitter (TX). The functions of the RX include:

- Input impedance control to minimize reflections.

- Signal conditioning to compensate for high frequency losses in the physical medium that cause inter-symbol interference (ISI).

- Recovering the clock rate of the incoming data using a clock and data recovery circuit (CDR) for protocols that do not transfer the clock.

- Correctly sampling the received data with the recovered clock.

- Deserializing received data into parallel streams at a lower speed.

- Detecting when the physical medium interface transitions from an idle state to an active state.

Figure 3: Block diagram of a PMA RX

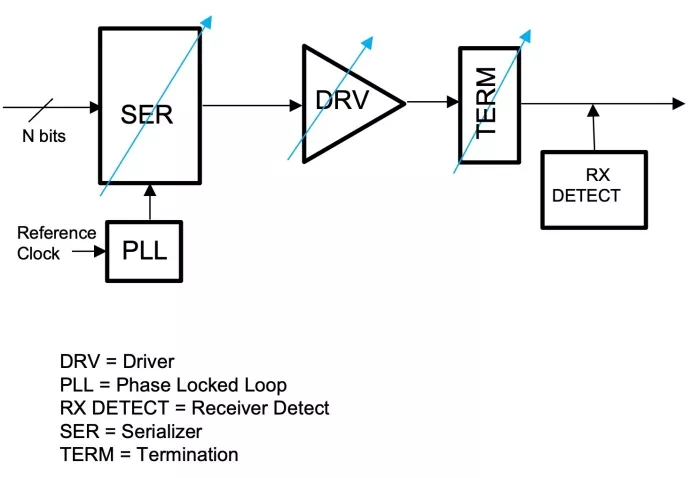

The primary functions of the TX include:

- Locking the transmit phase-locked loop (PLL) to a local reference clock.

- Serializing low speed data from the core to speeds appropriate for the physical medium.

- Driving the signal with a specific amplitude as prescribed by the protocol.

- Performing TX equalization using a finite-impulse-response (FIR) filter.

- Controlling output impedance to minimize reflections.

- Optionally, performing a detection of a valid far-end receiver termination.

Figure 4. Block diagram of a PMA TX

Common use cases for PMAs include communication:

- With a local processor over PCBs, backplanes, low-loss cabling, or fiber optic, as in the PCIe protocol.

- Through a video cable for DisplayPort or HDMI protocols.

- With peripheral devices using USB protocols.

- Between data converters and logic devices with JESD204B/C protocols.

- Between an image sensor and an SoC, as in the SLVS-EC protocol.

- Between a display or camera and an application processor in a mobile device, as in the MIPI D-PHY and C-PHY protocols.

Need for a Multi-Protocol PMA

Often an SoC developer requires a PMA that can address more than one protocol. In these cases, they would benefit from having a single silicon-proven multiprotocol PMA.

An MP-PMA has many advantages:

- It can be configured to address multiple protocols within one physical instance, allowing the SoC to have flexibility depending on the chip programming. This saves die area, package size and pin count, as well as integration effort. This directly translates to reduced costs.

- Reduces IP licensing cost by allowing different instances of the same MP-PMA to be used for different protocols on the same chip.

- Where protocols have the same electrical specifications, a single MP-PMA can reduce characterization time, resulting in lower overall project costs and reduced time to market.

- When the goal of the end product is protocol programmability, like in a Field-Programmable Gate Array (FPGA), the same PMA instantiation may be used for several different protocols.

Multi-Protocol PMA Requirements and Design Choices.

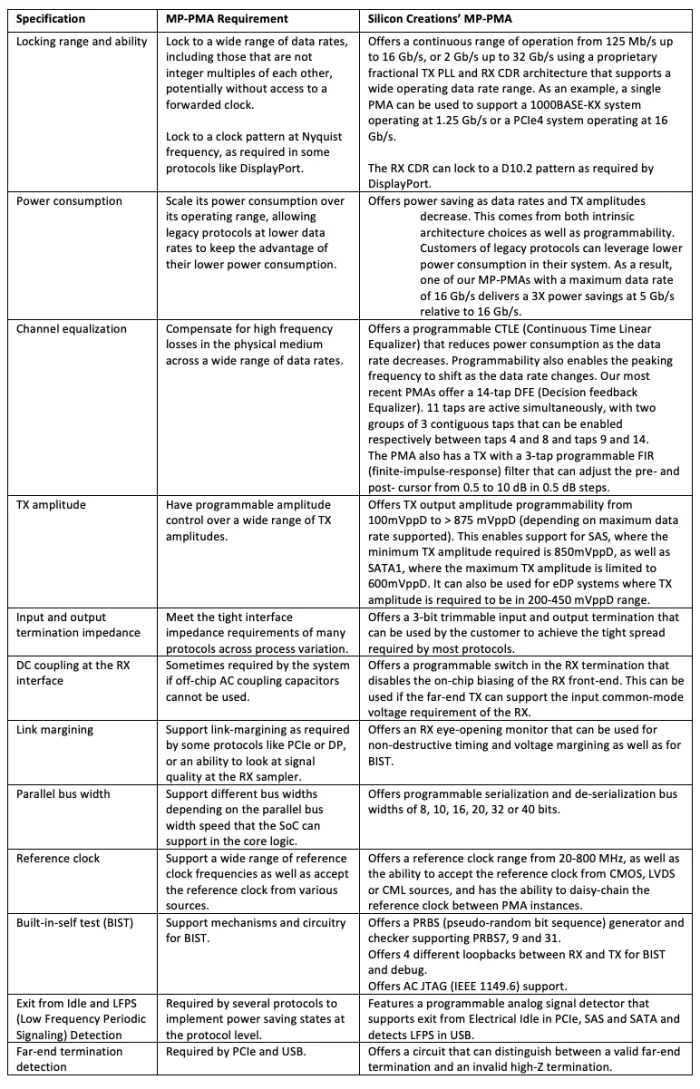

To service a wide range of protocols, careful thought must be given to every aspect of the PMA architecture. As a result, a versatile MP-PMA design must incorporate many specific features to support all the underlying requirements. The table below summarizes the requirements of an MP-PMA and how the Silicon Creations’ MP-PMA addresses these requirements.

Silicon Creations PMA Development History

At Silicon Creations, our MP-PMA development began with one of the most demanding of all multi-protocol applications – an FPGA. The transceivers in an FPGA need to work for many different protocols. Silicon Creations’ MP-PMA is used in Microchip’s PolarFire® FPGA family of products, which boasts the lowest power FPGA in its class. This is largely attributed to the Silicon Creations’ low power MP-PMA that supports, in the PolarFire device, PCIe Gen 1 and 2, Interlaken, 10GBASE-R, 10GBASE-KR, FC-8G, JESD204B, USXGMII, CPRI1-9, SATA, SDI, SGMII, 1000BASE-X, RXAUI, QSGMII, SLVS-EC, DisplayPort and CoaXPress. Following that development, Silicon Creations has developed MP-PMAs in various process nodes for many additional customers.

Multi-Protocol SoC Examples

As mentioned earlier, the MP-PMA provides an SoC designer targeting multiple protocols a single RX/TX that can reduce the IO count on their chip or reduce IP licensing costs by using multiple instances of the same MP-PMA for different ports. Some examples of customer requested protocol combinations are:

- PCIe4 + USB3.x SuperSpeed Bus + SATA for memory applications.

- PCIe4 + JESD204C for a Wifi SoC.

- V-by-One HS + DisplayPort + USB3.x SuperSpeed Bus in an SoC for display applications.

- 1000BASE-KX + 1000BASE-SX/LX + 100BASE-FX + SGMII for an SoC interface to optical transceivers and between the MAC and PCS in an Ethernet SoC.

Conclusion

An MP-PMA that addresses several serial data transmission protocols with a single programmable design offers significant advantages to SoC developers. The Silicon Creations’ MP-PMA is a power and area optimized, high-performance, highly programmable PMA that can support a wide range of protocols. It has been successfully deployed in Microchip’s PolarFire FPGA, a challenging application for an MP-PMA in terms of the number of supported protocols, as well as several other customer SoCs.

Reference: Protocol Acronyms

- DP: DisplayPort

- HDMI: High-Definition Multimedia Interface

- JESD204B/C: JEDEC Serial Interface for Data Converters

- LVDS: Low-Voltage Differential Signaling.

- MIPI: Mobile Industry Processor Interface

- PCIe: Peripheral Component Interconnect Express

- SGMII: Serial Gigabit Media-Independent Interface

- SLVS-EC: Scalable Low Voltage Signaling with Embedded Clock

- SAS: Serial Attached SCSI

- SATA: Serial Advanced Technology Attachment

- USB: Universal Serial Bus

Related Semiconductor IP

Related White Papers

- Debug and testability features for multi-protocol 10G Serdes

- How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

- IO and multiprotocol processing in highly demanding embedded architectures

Latest White Papers

- Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity