Accelerated SoC Verification with Synopsys Discovery VIP for the ARM AMBA 4 ACE Protocol

Synopsys Inc.

Abstract

— As the complexity and number of processor cores in SoC designs increase, so do the verification challenges. One such challenge is verifying hardware-based cache coherency protocols used by these multi-core SoCs.

Synopsys provides 100% SystemVerilog-based VIP that supports the ARM AMBA 4 AXI and ACE (AXI Coherency Extensions) protocols, as well as the UVM, VMM and OVM methodologies. Constrained-random sequences, protocol checks and coverage plans are also provided.

This paper describes how a reference verification platform built with the Discovery VIP for the AMBA ACE protocol can be utilized to accelerate the verification of multi-core SoCs. Also highlighted are Synopsys verification technologies like Discovery Visualization Environment (DVE) and Protocol Analyzer for advanced debug of the AMBA 4 AXI/ACE protocols.

Index Terms -- SoC Verification, SystemVerilog, Verification Intellectual Property (VIP), ARM AMBA 4 ACE Protocol, VMM, OVM, UVM, Multi-core.

I. INTRODUCTION

Multi-processor technology provides SoC architects with the flexibility to increase processing capabilities but still optimize for power consumption. But this flexibility at the SoC architecture phase adds more complexity to the SoC hardware verification phase, a part of the SoC product cycle already under pressure from ever decreasing time-to-market demands. One aspect of this complexity is that the coherency between processor caches are implemented, and therefore verified, in hardware.

Section II of this paper highlights the cache coherency challenge for multi-processor SoC designs, ARM’s hardware-based protocol solution to the problem and then finally the verification tasks associated with verifying SoC designs that use such a protocol.

Sections III and IV discuss Synopsys’ Discovery Verification IP (VIP) and Reference Verification Platform (RVP) for the AMBA 4 AXI/ACE protocol and how these are used to accelerate the verification of SoCs that use the AMBA ACE protocol.

Section V highlights two commercial design case studies for Broadcom and MediaTek.

II. CACHE COHERENCY VERIFICATION

In multi-processor designs, different values of a processor’s cache line may exist simultaneously in equivalent processor cache lines or external memory. The cache coherency challenge can be defined as ensuring all of these locations get the most up to date value when needed. Solutions to the cache coherency problem exist in both software and hardware implementations. The requirement for more power- efficient processing is driving the need for hardware based implementations.

To address the cache coherency requirement between their multi-core Cortexâ„¢ processors, ARM extended the AMBA AXI protocol to include AXI Coherent Extensions (ACE) [1].

Fig. 1. CoreLink CCI-400 Cache Coherent Interconnect for AMBA 4 ACE [2]

The AMBA AXI and ACE Protocol Specification document provides the additional description of the ACE protocol [3]. This specification defines the protocol in terms of processor cache line states and how changes to those states (represented by transactions) are communicated to other coherent components across the existing and additional AMBA AXI channel and signal interfaces. These definitions fit well with the object-oriented transaction based verification methodologies such as VMM, OVM and UVM.

Therefore, to verify a multi-processor SoC design that uses the hardware-based AMBA ACE protocol, the typical verification practices of 1) random stimulus generation, 2) signal assertion and scoreboard based checking and 3) functional coverage and planning, can be applied.

III. DISCOVERY VIP FOR AMBA 4 AXI/ACE PROTOCOLS

Synopsys provides a 100% SystemVerilog-based VIP suite that supports the ARM AMBA 4 AXI and ACE protocols. This section discusses two features of the suite that will help reduce verification time and also improve confidence in the design’s correctness.

First, the suite provides VIP models for the AMBA master, slave and interconnect components. With VIP models available for all components, including the interconnect, the verification team can assemble a fully functional AMBA design and testbench, including testcases, before any RTL models are available. When an RTL model is available, it can replace the VIP model, or the VIP model can be placed in monitor-only mode beside the RTL model. Model substitution can be done with any combination of the master, slave and interconnect models. This allows testing of the RTL models to begin sooner since the testbench is already passing coherent transactions between the masters, interconnect and slaves.

Second, the suite also provides a system-level environment that automatically creates, instantiates, configures and connects multiple master and slave VIP components with an interconnect VIP component, based on values in a system-level configuration. The environment can also instantiate and enable a system-level monitor and (virtual) sequencer, also based on configuration values. All the user needs to do is create and assign values to the environment’s configuration object. This automatic function of the environment not only reduces the time to manually create an environment, it also removes the chance of a manual coding error, which would impact the project debug time.

Fig. 2. Synopsys Discovery VIP for AMBA AXI/ACE Protocol

IV. REFERENCE VERIFICATION PLATFORM (RVP) FOR AMBA 4 ACE PROTOCOL

Synopsys also provides a Reference Verification Platform (RVP) for the AMBA AXI/ACE protocol. This section discusses how the RVP will also accelerate the verification of an SoC which uses the AMBA ACE protocol.

The RVP contains a pre-configured system-level environment, as discussed in the previous section. It also provides testcases using a constrained-random, coverage-based, UVM methodology within VCS/VCS-MX simulation.

Fig. 3. Reference Verification Platform for AMBA AXI/ACE Protocol

The following sections provide more detail on the features that the RVP provides, including configuration, stimulus generation, protocol monitoring and checking, and coverage planning and closure.

A. Configuration

The RVP provides an initial configuration common to the most ARM SoC designs. The configuration contains 3 master VIPs (2 AMBA ACE, 1 AMBA ACE-Lite) and one slave VIP (AMBA ACE-Lite) connected to an interconnect VIP. The Interconnect VIP is not restricted to any number of masters, slaves or functionality, but the initial configuration allows the user to see a working example. Should the user need a different number of masters, slaves and features, they can easily change the configuration. When the simulation is re-run, using the simulation scripts provided, the system environment will create the new topology automatically. It is recommended that the user explore all capabilities of the RVP first before changing the configuration.

B. Stimulus Generation

All Discovery VIP provide pre-written input stimulus in the form of either UVM/OVM sequences or VMM scenarios, otherwise known as collections or libraries. The VIP for the AXI/ACE protocol provides these both at the master/slave port level as well as the system level, the latter referred to as a virtual sequencer or multi-stream scenario generator. The RVP configures the port and system level generators to use a selection of stimuli from these collections. Examples of master port level sequences include Blocking Write-Read and Write Data Before Address sequences. Examples of a system level sequence would be a single coherent transaction like WriteLineUnique or a multi-transaction sequence like Snoop During Memory Update. Since the framework to use these input stimuli is already written, the user needs only to substitute other sequences/scenarios that reflects their verification goals.

C. Protocol Monitoring and Checking

Discovery VIP provides port level checks in a port level monitor, a component that exists in the slave and master. read_data_chan_readclean_resp_valid_check is one example that verifies the IsShared and PassDirty signals are correctly asserted in response to a ReadClean transaction. System-level checks are also provided in a system level monitor. One example is the no_two_cachelines_in_dirty_state check that verifies that no two masters have the same cache line in the Dirty state. Port and system level checks are enabled by default in the VIP and RVP so no changes are required by the user unless they want those disabled. The checks are also configuration aware so the user does not need to modify the environment should any configuration changes be made.

D. Environment and Protocol Debug

Synopsys provides a selection of methodology-aware features in the Discovery Visualization Environment (DVE) tool. The RVP illustrates how DVE can be used to debug AMBA ACE protocol errors encountered at the signal or transaction level.

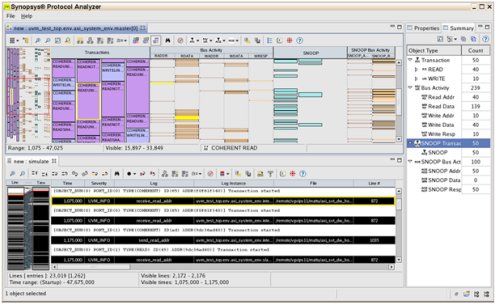

Synopsys also provides another tool called DiscoveryTM Protocol Analyzer (PA) with all Discovery VIP. PA allows the user to analyze and debug a protocol at a transaction level timeline view, while also synchronizing to the more traditional waveform and UVM/VMM/OVM message level. The RVP shows users how to analyze and debug the AMBA AXI/ACE protocol in a working simulation.

Fig. 4. Synopsys Discovery Protocol Analyzer

E. Coverage Planning and Closure

Similar to the protocol checks, the VIP provides AMBA ACE protocol coverage in the master/slave port monitors, and system level monitor. Toggle, state and delay coverage is provided at the port level, is configuration-aware, and disabled by default. Transaction cross coverage is provided at the master/slave level, configuration-aware and enabled by default.

The Discovery VIP also provides Verification Planner sub-plans from the AMBA ACE master, slave and interconnect point of view. These sub-plans back-annotate and amalgamate the previously mentioned VIP coverage to specific features of the AMBA AXI and ACE Protocol Specification [3]. Within the RVP, as more complex ACE protocol sequences are executed, the user will be able to analyze the increasing coverage until the coverage goals are met.

V. COMMERCIAL DESIGN CASE STUDIES

Broadcom faced the challenge of verifying cache coherency latency with multiple big.LITTLE design configurations, limited engineering resources and tight schedule. Using the Discovery VIP and RVP, they were able to quickly implement an AMBA 4 AXI/ACE environment that allowed them to focus on functional coverage and debug to ensure a predictable product while still meeting their project schedules. [4]

Mediatek not only wanted to migrate from Synopsys’ Open-Vera based VIP for AMBA AXI protocol, to the new SystemVerilog VMM VIP, but also to using the new AMBA ACE protocol. MediaTek was able find bugs in their design in a short period time by constructing and using complex VMM Multi-Stream Scenarios (MSS) and built-in cache coherent checkers provided by the new Discovery VIP and RVP. [5]

VI. CONCLUSION

As the number of ARM processor-based multi-processor SoC designs using the AMBA ACE protocol for cache coherency increases, so does the need to verify these designs with predictability while speeding the time-to-market. As discussed in this paper, SoC teams can quickly achieve this by using the Synopsys Discovery VIP and Reference Verification Platform for AMBA AXI/ACE protocol.

REFERENCES

[1] A. Stevens, Introduction to AMBA 4 ACEâ„¢, [White Paper]. Retrieved from http://www.arm.com/files/pdf/CacheCoherencyWhitepaper_6June2011.pdf

[2] ARM, CoreLink CCI-400 Cache Coherent Interconnect for AMBA 4 ACE [Web Site] Retrieved from http://www.arm.com/images/CoreLink_400_Series.jpg

[3] ARM, “AMBA AXI and ACE Protocol Specificationâ€, ARM IHI 0022D, Issue D, 28 October 2011. Retrieved from https://silver.arm.com/download/download.tm?pv=1198016

[4] N. Shah (Broadcom), “AXI and ACE Verification for CortexTM-A Seriesâ€, DAC 2012

[5] W. Huang, S. Chou, (MediaTek) “Creating AMBA 4 ACE Test Environment with Discovery VIPâ€, SNUG Taiwan 2012

Related Semiconductor IP

- NPU IP Core for Mobile

- MSP7-32 MACsec IP core for FPGA or ASIC

- UHF RFID tag IP with 3.6kBit EEPROM and -18dBm sensitivity

- NPU IP Core for Edge

- Specialized Video Processing NPU IP

Related White Papers

- AMBA 4 ACE for Heterogeneous Multiprocessing SoCs

- PCIe IP With Enhanced Security For The Automotive Market

- Smart way to memory controller verification: Synopsys Memory VIP

- Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

Latest White Papers

- Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity