Thalia Design Automation launches AMALIA Platform 25.2

Revolutionary AI-powered platform delivers advanced electromigration compliance and streamlined Key Devices integration

Cwmbran, United Kingdom – July 16, 2025 – Thalia Design Automation today announced the release of AMALIA 25.2, a groundbreaking evolution of its industry-leading analog and mixed-signal IP reuse platform. This major release introduces the fully integrated Design Pre-Trained Transformer (DPT) AI engine, advanced electromigration compliance workflows, and strategically repositioned Key Devices identification that collectively transform the semiconductor design migration landscape.

AI engine integration transforms analog IC design migration

The Design Pre-Trained Transformer (DPT), first introduced earlier this year, now serves as the core AI engine powering the entire AMALIA Platform. This sophisticated, pre-trained system enables AMALIA to be trained seamlessly to customer environments with different foundries and nodes enabling fine-tuning for specific design migration scenarios. By intelligently analyzing both source design schematics, layouts and process design kits (PDKs), DPT extracts critical process and circuit features to drive smart migration decisions —dramatically accelerating the path for design migration.

Advanced electromigration compliance ensures reliability

AMALIA 25.2 introduces a powerful new electromigration compliance feature that automatically adjusts power and ground buses during layout porting. Through sophisticated analysis of current density and sheet resistance, the system ensures migrated designs meet stringent EM constraints across advanced nodes, including FinFET technologies. This capability significantly reduces the risk of failures in next-generation semiconductor designs while supporting an extensive range of process technologies.

Strategic Key Devices enhancement accelerates workflow

The enhanced Key Devices capability has been expanded and strategically repositioned from the Design Enabler module to the earlier Circuit Porting Pro module within the migration workflow. This feature ensures performance-critical components are identified and preserved from the very beginning of the migration process, eliminating costly design iterations and maintaining design intent throughout the entire workflow.

Industry leadership in analog IP migration

“AMALIA 25.2 delivers breakthrough capabilities that can improve engineer throughput by an order of magnitude," said Sowmyan Rajagopalan, CEO at Thalia Design Automation. "Features like advanced inductor analysis, schematic migration with parasitic preservation, and intelligent metal stacking are true game changers. As pioneers in analog migration, we're continuously expanding our platform to support the increasingly complex demands of modern semiconductor design."

The release underscores Thalia's commitment to pushing the boundaries of semiconductor design automation, delivering solutions that address the increasingly complex challenges of advanced node migration while maintaining the precision and reliability that analog and mixed-signal designs demand.

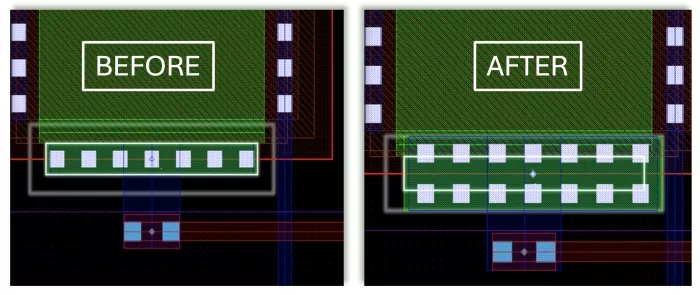

Figure 1: Electro Migration Fixer in AMALIA 25.2

The two screenshots illustrate the before and after for a small section of a migrated design.

For this illustration, the source and target design use a generic PDK for a 90nm and 45nm process respectively.

The Current Density Source to Target is 2, i.e. the source technology supports twice the current for same metal width compared to the target technology.

After selecting a particular metal layer and running the Electro Migration Fixer feature AMALIA intelligently understands it needs to increase the metal width 2X and where required increase the number of vias.

About Thalia Design Automation

Since 2011, Thalia Design Automation has pioneered semiconductor IP design migration solutions, empowering industry leaders through innovative, bespoke approaches to analog, mixed-signal, and RF IC design migration. The company continues to drive industry transformation through cutting-edge automation technologies that accelerate time-to-market while ensuring design integrity.

For more information, visit thalia-da.com

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related News

- Thalia enhances AMALIA Platform with new AI models to revolutionize analog, RF and mixed-signal IC design migration

- Thalia Design Automation announces AMALIA Platform release 25.3 qualified for advanced process nodes down to 4nm

- Thalia Design Automation successfully delivers voltage regulator in a 22nm process node with 45% reduction in design time using its AMALIA software

- Thalia's AMALIA Technology Analyzer de-risks Analog IP reuse for major IP houses and IC manufacturers

Latest News

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025

- Omnitrx introduces Omni500 Ethernet Evaluation Platform, Built on Comcores Expertise

- Three Misconceptions About the $402B Semiconductor Foundry Industry