SiFive’s New RISC-V IP Combines Scalar, Vector and Matrix Compute to Accelerate AI from the Far Edge IoT to the Data Center

New X100 Series Joins Upgraded X200, X300 and XM IP to Address Growing Demand for RISC-V AI Solutions

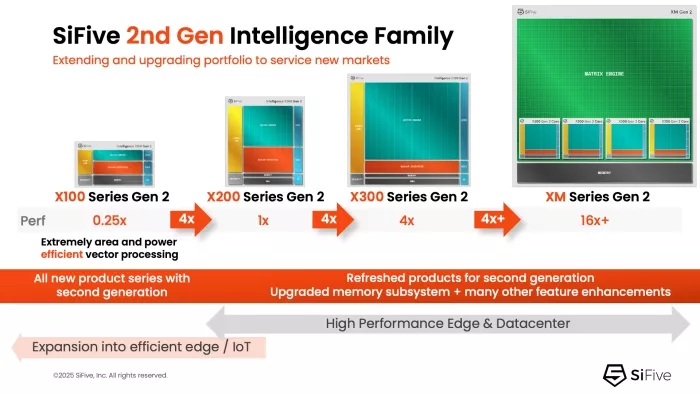

Santa Clara, Calif. – Sept. 8, 2025 – Further expanding SiFive’s lead in RISC-V AI IP, the company today launched its 2nd Generation Intelligence™ family, featuring five new RISC-V-based products designed to accelerate AI workloads across thousands of potential applications. The lineup includes two entirely new products—the X160 Gen 2 and X180 Gen 2—alongside upgraded X280 Gen 2, X390 Gen 2 and XM Gen 2. These new products all feature enhanced scalar, vector and, specifically with XM, matrix processing capabilities designed for modern AI workloads.

The X160 Gen 2 and X180 Gen 2 target far edge compute and IoT applications, achieving high efficiency in a compact footprint and delivering advanced AI functionality to the deeply embedded edge, which is heavily constrained by power and area. Target industries include automotive, autonomous robotics, industrial automation, and smart IoT.

“AI is catalyzing the next era of the RISC-V revolution,” said Patrick Little, CEO of SiFive. “We're seeing strong traction including adoption of the new X100 series by two Tier 1 U.S. semiconductor companies. Our new 2nd Generation Intelligence IP builds on this momentum, adding new features and configurability to accelerate our customers’ designs and time to market.”

Fast Growing Opportunity

A Deloitte survey predicts at least 20% AI workload growth in every tech environment, including 78% growth in AI edge computing. “SiFive is investing to take advantage of the tremendous growth that is occurring in edge AI compute, innovating in markets that need more focus and optionality,” said Pat Moorhead, Founder, CEO and Chief Analyst, Moor Insights and Strategy. “The new SiFive Intelligence Gen 2 products bring several novel features that could solve real customer problems and bring solid solutions with unique methods of performance and efficiency.”

Vector Processing Advantage

Vector engines process multiple data items in parallel, reducing instruction overhead and power consumption. SiFive's vector-based RISC-V IPs strike the right balance between efficiency, configurability and performance. Compared to traditional scalar only CPUs, vector CPUs can run AI models faster, with a smaller footprint and lower power consumption—ideal for edge AI applications.

Real-World Applications

Advanced AI Computation: From narrow to wide vector engines, to XM with a highly scalable Matrix engine, SiFive’s 2nd Generation Intelligence IP offers customers a wide range of performance, area and power options within a single scalable ISA as AI permeates all markets and form factors.

Accelerator Control and Assist: All X-Series IPs can function as an Accelerator Control Unit (ACU), providing control and assist functions for a customer’s accelerator engine via specialized co-processor interfaces (SSCI and VCIX). This allows customers to focus on data processing innovations at the platform level and simplifies the software stack.

Available Now

All five Intelligence Gen 2 products are available for licensing immediately, with first silicon expected in Q2 2026.

For more details, watch SiFive Chief Architect Krste Asanovic here.

SiFive will showcase these new products at the AI Infra Summit in Santa Clara, Calif., from Sept. 9-11 in booth #908.

For technical specifications view the Product Briefs: X160 Gen 2, X180 Gen 2, X280 Gen 2 and X390 Gen 2, or the Intelligence Family Brief.

About SiFive

SiFive is the leader in RISC-V computing, delivering the custom silicon foundation that AI demands. As the gold standard for RISC-V CPUs, SiFive combines the flexibility of open standards with unmatched performance, enabling scalable AI solutions from the edge to the data center. With the broadest portfolio, industry-leading IP, and deep system expertise, SiFive helps the world’s leading technology companies rapidly build differentiated AI hardware—faster, at lower cost, and without compromise.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- SiFive and Kinara Partner to Offer Bare Metal Access to RISC-V Vector Processors

- SiFive Collaborates with Red Hat to Support Red Hat Enterprise Linux for RISC-V

- Tenstorrent Productizes RISC-V CPU And AI IP

- Upbeat Technology and SiFive Introduce Next-Gen Ultra-Low Power RISC-V MCU with AI Acceleration

Latest News

- Rebellions Collaborates with SK Telecom and Arm Targeting Sovereign AI and Telecom Infrastructure

- Sarcina Launches UCIe-A/S Packaging IP to Accelerate Chiplet Architectures

- BrainChip Unveils Radar Reference Platform to Bridge the ‘Identification Gap’ in Edge AI

- Siemens accelerates AI chip verification to trillion‑cycle scale with NVIDIA technology

- SiFive Raises $400 Million to Accelerate High-Performance RISC-V Data Center Solutions; Company Valuation Now Stands at $3.65 Billion