Mentor Graphics Adds Memory Models to Create Industry's First Complete UVM SystemVerilog Verification IP Library

WILSONVILLE, Ore., February 29, 2016 – Mentor Graphics Corporation (NASDAQ: MENT) today announced availability of the first entirely native UVM SystemVerilog memory verification IP library for all commonly used memory devices, configurations, and interfaces. Mentor is adding over 1600 memory models to the Mentor® Verification IP (Mentor VIP) library that already supports over 60 commonly used peripheral interfaces and bus architectures. As a result, Mentor becomes the first company to supply ASIC and FPGA SoC designers with a complete UVM SystemVerilog verification IP library that covers the breadth of their peripheral interface, bus protocol and memory device needs. Providing the complete library in one consistent industry-standard format reduces the time it takes for engineers to set up verification runs, so they can focus on verifying unique, high-value parts of their designs.

The new memory library supports a wide spectrum of memory model variations including leading-edge protocols such as the high-bandwidth, low-pin-count HyperBus™ interface for HyperRAM™ and HyperFlash™ memory devices. It also supports a full range of dynamic RAM models including DDR4, Low Power DDR4, Hybrid Memory Cube, High Bandwidth Memory-2, and the new JESD229-2 Wide I/O-2 standard. Finally, it includes a full complement of flash memory models including SDIO 4.1, SDCard 4.2, eMMC 5.1, ONFI 4.0, UFS, and serial, toggle, NAND and NOR flash.

“We’re excited about Mentor Graphics’ release of its extensive memory verification IP model library, in particular its support for the new HyperBus interface,” said Jackson Huang, Vice President of Segment and Ecosystem Marketing at Cypress Semiconductor Corp. “We developed the HyperBus interface to achieve our increasing product performance goals with faster response times, without sacrificing breadth of functionality.”

Verification IP helps engineers reduce the time spent building testbenches by providing re-usable building blocks for common interfaces, protocols, and architectures. Mentor’s memory verification IP model library includes memory configuration software that allows customers to instantly generate fast, timing-accurate, validated memory models based on vendor, protocol, and part number. In addition, Mentor’s unique “reconfigurable-on-the-fly” architecture helps them evaluate second sources without recompilation or even restarting simulations.

“The vast majority of ASIC and FPGA project teams have moved to standard UVM SystemVerilog verification methodology, and until now have been unable to find a universal VIP library that supports bus protocols, peripheral interfaces, and memory devices, all in native UVM,” says Mark Olen, Mentor Graphics product marketing manager, Design Verification Technology Division. “Judging from initial adoptions of our new memory VIP library, it’s easy to see why verification IP is one of the fastest growing sub-segments in the functional verification market, now exceeding $110 million in annual spending, according to the Electronic Design Automation Consortium.”

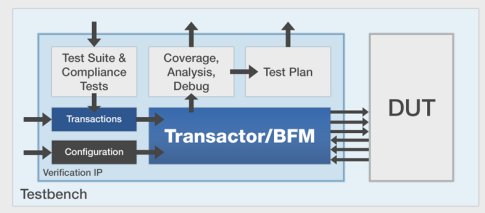

The Mentor VIP library provides engineers with standard UVM SystemVerilog components using a common architecture across all supported protocols. This allows rapid deployment of multiple protocols within a verification team. Test plans, compliance tests, test sequences and protocol coverage are all included as SV and XML source code, allowing simple re-use, extension and debug. The Mentor VIP components also include a comprehensive set of protocol checks, error injection and debug capabilities. The new memory models are qualified on all industry-standard simulators.

Mentor VIP is a core technology in the Mentor Enterprise Verification Platform™ (EVP) which boosts productivity in SoC functional verification for both ASICs and FPGAs by combining advanced verification technologies in a comprehensive platform. The Mentor EVP combines Questa® advanced verification solutions, the Veloce® emulation platform, and the Visualizer™ debug environment into a globally accessible, high-performance, datacenter resource. The Mentor EVP features global resource management that supports project teams around the world, maximizing both user productivity and total verification return on investment.

About Mentor Graphics

Mentor Graphics Corporation is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the world's most successful electronic, semiconductor and systems companies. Established in 1981, the company reported revenues for the fiscal year ending January 31, 2015, of approximately $1.2 billion. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Related Semiconductor IP

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

Related News

- Paradigm Works Announces SystemVerilog FrameWorks Template Generator Support for UVM

- EVE's ZeBu SystemVerilog Approach Used by Fujitsu Kyusyu Network Technologies to Implement UVM Co-Emulation

- Aldec's Active-HDL Verification Capabilities Enhanced to Support SystemVerilog Constructs and UVM

- Synopsys Donates Key Verification Technologies to Accellera's SystemVerilog 3.1 Standard

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025