The DTPCI32DC - Dual Clock 32bit PCI Bus Target Interface from Digital Core Design

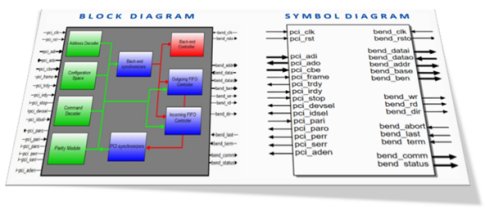

Bytom, July the 14th, 2016. The DTPCI32DC is a 32-bit target interface which meets all requirements of the PCI 3.0 specification for a target device. It compromises a minimal gate count with a high-bandwidth data transfer. The Core’s main feature is the presence of two clock domains. - They enable flexibility and higher performance as well – says Tomek Krzyzak, VCEO of DCD – When time required for implementation becomes crucial, the DTPCI32DC brings a domain crossing. Saved time can be used for a specific system implementation instead. The user-friendly back-end interface can be very easily and effectively tailored to the design needs.

The Core supports up to six Base Address Registers and Expansion ROM address register with both I/O and Memory space decoding from 16 bytes up to 4 GB. Another important feature is a cache wrapping hardware support and a cacheline pre-fetching capability. The DTPCI32DC is accepting size cache lines which are powered from 2 up to 128. It enables also target-disconnect with data, without data or by a target abort. Moreover, the DTPCI32DC is capable to work with 66 MHz clock frequency in the most popular technologies. It assures the PCI timing requirements, as well as other parameters like FIFOs depths number or Base Address Registers (they can be easily configured at the pre-synthesis stage).

More information & evaluation requests: http://dcd.pl/ipcore/1112/dtpci32dc/

Key Features:

- Fully supports PCI specification 3.0 protocol

- Stable clock domain crossing regardless of the clock frequencies

- Cache wrapping (cache lines must be powers of 2)

- User controlled burst data transfer

- Possible no-wait state transactions

- Automatic handling of configuration space read/write access

- Parity generation and parity error detection

- Single interrupt support

- Configurable FIFOs depth

- Supported backend initiated burst termination (with and without data)

- No tri-state buffers

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related News

- DCD-SEMI Joins MIPI Alliance and Unveils Latest I3C IP at MIPI Plugfest Warsaw 2025

- DCD-SEMI Brings Full ASIL-D Functional Safety to Entire Automotive IP Cores Portfolio

- DCD-SEMI Unveils Ultra-Fast DAES IP Core for AES Encryption

- DI3CM-HCI, A High-Performance MIPI I3C Host Controller IP Core for Next-Generation Embedded Designs

Latest News

- Rebellions Collaborates with SK Telecom and Arm Targeting Sovereign AI and Telecom Infrastructure

- Sarcina Launches UCIe-A/S Packaging IP to Accelerate Chiplet Architectures

- BrainChip Unveils Radar Reference Platform to Bridge the ‘Identification Gap’ in Edge AI

- Siemens accelerates AI chip verification to trillion‑cycle scale with NVIDIA technology

- SiFive Raises $400 Million to Accelerate High-Performance RISC-V Data Center Solutions; Company Valuation Now Stands at $3.65 Billion