Barcelona Zettascale Lab advances European technological sovereignty as Cinco Ranch TC1 chip passes validation

Tests confirm the robustness of the new open-source chip architecture, positioning the BSC-led lab among Europe’s leaders in advanced computing

Fabruary 9, 2026 -- The Barcelona Zettascale Lab (BZL), a project led by the Barcelona Supercomputing Center – Centro Nacional de Supercomputación (BSC-CNS), has successfully completed the experimental bring-up of the Cinco Ranch TC1 chip. The results confirm the robustness of the design and the viability of its, based on open-source RISC-V based computing architecture. This milestone represents a key step in the chip development process and marks a qualitative leap on the path toward sovereign supercomputing technologies in Europe.

The results demonstrate not only a high level of performance and maximum energy efficiency, but also the ability of the BZL and its strategic partners to position themselves at the forefront of semiconductor design. The new chip offers an open, flexible alternative free from dependence on the proprietary architectures of large multinational corporations, reinforcing the role of the BSC-led laboratory as a key player in the European advanced computing ecosystem.

The results demonstrate not only a high level of performance and maximum energy efficiency, but also the ability of the BZL and its strategic partners to position themselves at the forefront of semiconductor design. The new chip offers an open, flexible alternative free from dependence on the proprietary architectures of large multinational corporations, reinforcing the role of the BSC-led laboratory as a key player in the European advanced computing ecosystem.

“Successfully booting Linux in a stable manner and verifying that the chip reaches the expected frequencies confirms the maturity of the design and the quality of the work carried out by the BZL teams,” says Miquel Moretó, BSC researcher and coordinator of hardware activities at the Barcelona Zettascale Lab.

The Cinco Ranch TC1 is the first chip manufactured in an academic environment using the advanced 3-nanometer Intel 3 technology, one of the most advanced nodes currently available, enabling faster and more efficient chips thanks to greater transistor miniaturization. During the design phase, and due to the inability to access this technology directly, the BZL conducted internal evaluations on a comparable node, allowing the design to be thoroughly validated prior to final implementation.

Explore RISC-V IP

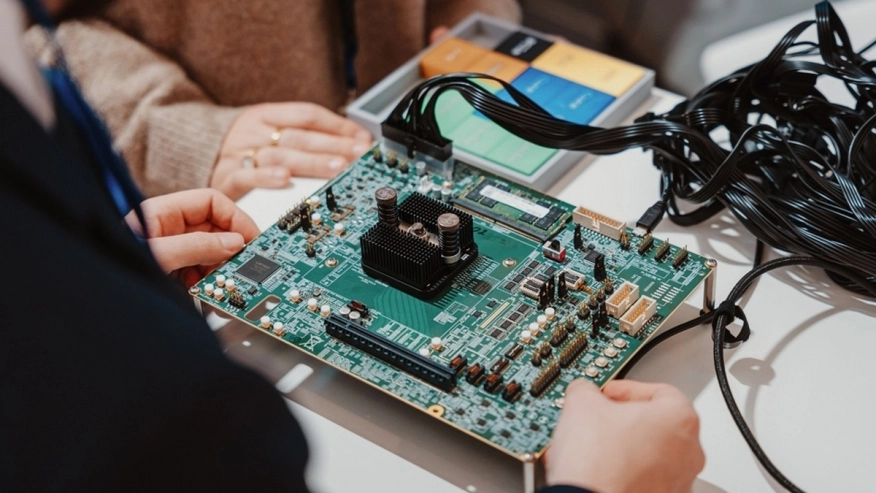

The internal organization of the Cinco Ranch TC1 is based on three complementary processing blocks, designed to work together and cover different computing profiles. This architecture defines how the different parts of the chip are organized and collaborate to perform tasks efficiently. The bring-up phase was carried out on the Hawk Canyon V2 evaluation board, developed by Intel for the initial validation of the chip once manufactured. After this first stage, the process will continue with functional and performance testing, software optimization, and full system validation, key steps to ensure stable chip operation.

Experimental validation of the TC1 chip on the Hawk Canyon board

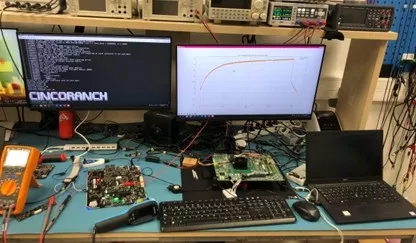

In May 2025, Linux was successfully booted on the Cinco Ranch TC1, and in July 2025, following the receipt of a batch of 500 chips, characterization and validation activities began. These activities consist of systematically verifying correct chip operation, measuring performance and efficiency, and confirming that specifications are met before deployment in real environments.

The results show a high rate of fully functional chips and confirm that the TC1 chip can operate at up to 1.25 billion cycles per second (1.25 GHz), a processing speed that exceeds the initial estimates made during the design phase.

Subsequent electrical and functional tests, including power consumption and temperature measurements as well as the execution of standardized benchmarks that measure chip speed and efficiency, are enabling the evaluation of its behaviour in real-world tasks and laying the groundwork for software optimization.

The successful bring-up of the Cinco Ranch TC1 represents a fundamental milestone for the BZL, confirming the viability of the developed architecture and strengthening its outlook toward future generations of advanced computing systems, while contributing to the reinforcement of Barcelona’s innovation ecosystem in semiconductor design led by the BSC.

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related News

- Europe Achieves a Key Milestone with the Europe’s First Out-of-Order RISC-V Processor chip, with the eProcessor Project

- S2C, MachineWare, and Andes Introduce RISC-V Co-Emulation Solution to Accelerate Chip Development

- The BSC coordinates the manufacture of the first open source chip developed in Spain

- BSC, Codeplay and SiFive help accelerate applications on RISC-V thanks to V-extension support in LLVM

Latest News

- Arasan Announces immediate availability of its UFS 5.0 Host controller IP

- Bolt Graphics Completes Tape-Out of Test Chip for Its High-Performance Zeus GPU, A Major Milestone in Reducing Computing Costs By 17x

- NEO Semiconductor Demonstrates 3D X-DRAM Proof-of-Concept, Secures Strategic Investment to Advance AI Memory

- M31 Collaborates with TSMC to Achieve Tapeout of eUSB2V2 on N2P Process, Advancing Design IP Ecosystem

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs