network-on-chip IP

Filter

Compare

17

IP

from

12

vendors

(1

-

10)

-

Network-on-Chip (NoC)

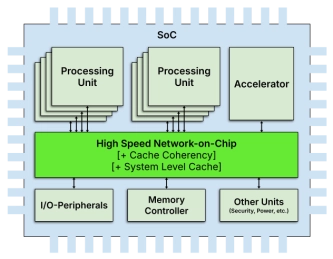

- InfiniNoC is a highly customizable Network-on-Chip (NoC) from InfiniNode Technologies, designed to provide a scalable, high-performance communication backbone for next-generation SoCs.

- It enables seamless integration of diverse IP blocks while delivering the flexibility, scalability, and performance required to accelerate complex chip development.

- The architecture supports high bandwidth and low latency alongside energy-efficient data movement, and it can be customized to match specific use cases and requirements.

-

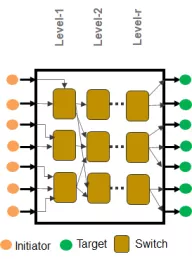

Smart Network-on-Chip (NoC) IP

- Smart NoC automation

- Topology generation with minimum wire length

- Scripting-driven regular topology creation

- Incremental design capability

- Auto-timing closure assist

-

Network-on-Chip (NoC) Interconnect IP

- AMBA AXI / APB / AHB protocol compliant

- Configurable number of masters and slaves

-

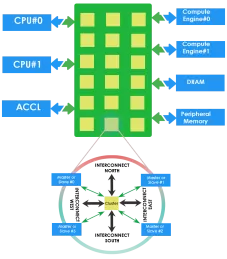

Coherent Network-on-chip (NoC) IP

- Layered, scalable, configurable, and physically aware configurable NoC

-

-

Coherent Network-on-Chip (NOC)

- Node Protocols: ACE4, ACE5 and CHI

- Architected to significantly reduce routing congestion for many-core systems

- Integrated with SkyeChip’s Home Agent and swappable with any other proprietary coherency handlers

- Supports operating frequencies up to 2GHz with assists in high frequency timing closures

-

Non-Coherent Network-on-Chip (NOC)

- Node Protocols: AXI4, AXI5, AXI-Stream, APB and proprietary protocols

- Architected to reduce routing congestion and to ease high frequency timing closure

- Supports operating frequencies up to 2GHz

- Supports source synchronous and synchronous clocking topologies

-

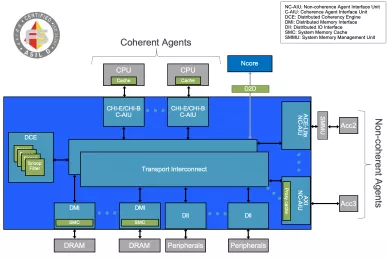

Ncore 3 Coherent Network-on-Chip (NoC)

- Supports multiple coherent agents, including Armv9 and RISC-V CPU clusters

- AMBA CHI-E, CHI-B and ACE interoperability, as well as ACE-Lite and AXI

- Low-latency proxy caches for efficient and quick integration of hardware accelerators into the coherent domain

- Configurable last-level caches

-

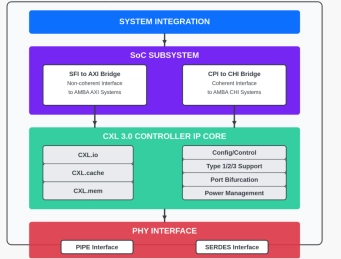

CXL 3.0 Controller

- The CXL Controller IP is micro-architected with power, performance, and area optimization for high bandwidth, minimum latency, and low power applications.

- The CXL IP supports seamless transition from FPGA prototyping to production silicon implementation.

- Featuring native integration with SignatureIP's Coherent and Non-coherent Network-on-Chip (NoC) IPs, this controller enables robust SoC subsystems and complete platform solutions

-

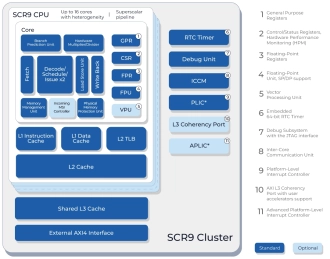

High-performance Linux-capable application core with a 12-stage dual-issue out-of-order pipeline, a VPU, cache coherency, and a hypervisor

- SCR9 is a high-performance, silicon-proven, Linux-capable 64-bit RISC-V processor core for entry-level server-class applications and personal computing devices.

- The SCR9 core supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, "V" Vector Operations, "B" Bit Manipulation, and "K" Scalar Cryptography extensions.