interlaken IP

Filter

Compare

25

IP

from

9

vendors

(1

-

10)

-

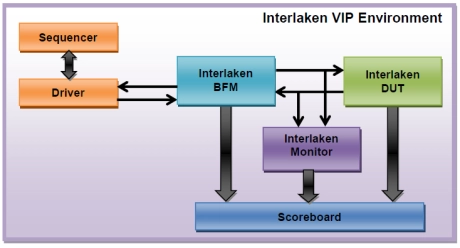

Interlaken Verification IP

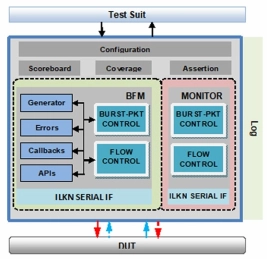

- INTERLAKEN VIP is reusable, highly configu rable, pre-verified, plug-and-play verification component developed in System Verilog - UVM, which is solution for networking based SoC incorporating INTERLAKEN packet interface protocol at Module, Chip and System level.

- INTERLAKEN VIP is developed using System Verilog, the unified language for Design & Verification and UVM reusable verification methodology.

-

Interlaken Intel® FPGA IP

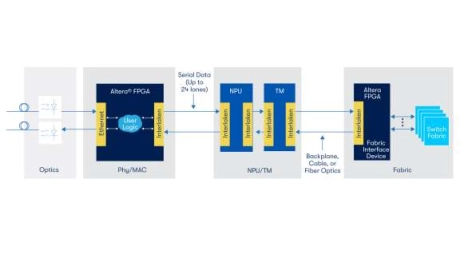

- The Interlaken Intel® FPGA IP core is Interlaken Protocol Definition v1.2 compliant and allows system developers to achieve high bandwidth throughput in their systems

- This pre-built, ready-to-go IP building block shortens the design cycle resulting in faster time to market.

-

Interlaken Look-Aside Intel® FPGA IP

- Interlaken Look-Aside is a scalable protocol that allows interoperability between a datapath device and a look-aside coprocessor for short, transaction-related transfers

- A look-aside coprocessor is connected "to the side" of the datapath, and is not in-line of the main datapath of the switch, router, or other networking device

- Interlaken Look-Aside is not directly compatible with Interlaken and can be considered a different operational mode.

-

Interlaken Verification IP

- Implemented natively in OpenVera, Verilog, SystemC, Specman E and SystemVerilog.

- Follows Interlaken specification as defined in Interlaken protocol definition v1.2.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Compliant to Interlaken protocol specification v1.2

-

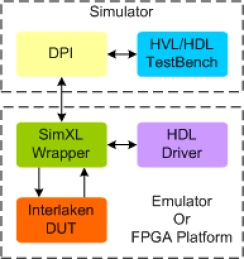

Interlaken Synthesizable Transactor

- Follows Interlaken specification as defined in Interlaken protocol definition v1.2

- Supports Interlaken look aside protocol specification v1.0

- Supports Interlaken retransmission extension specification 1.1

- Supports multi-channel implementation as per the specification

-

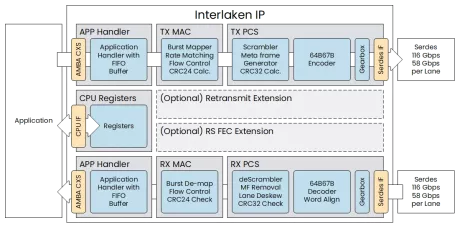

INTERLAKEN IIP

- Compliant with Interlaken protocol specification v1.2

- Interlaken look as side protocol 1.1

- Interlaken retransmission extension specification 1.2

- Interlaken Reed-Solomon Forward Error Correction Extension 1.1

-

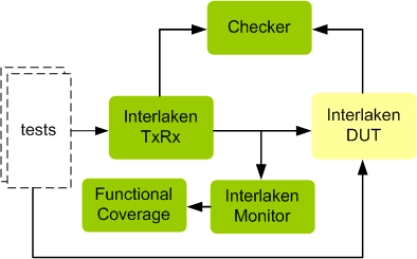

Interlaken Verification IP

- Compliant to Interlaken Protocol Specification Rev 1.2, Interlaken Look-Aside Protocol Definition Rev 1.1, Interlaken Retransmit Extension Protocol Definition Rev 1.2, Interlaken Interoperability Recommendation v 1.9.

- Complainto theReed Solomon Forward Error Correction Extension 1.0

- Configurable BurstMax, BurstMin, BurstShort size, Meta Frame Length, Channel ON/OFF.

- Configurable Number of lanes. Up to 64K channels using Multi-Use bits.

-

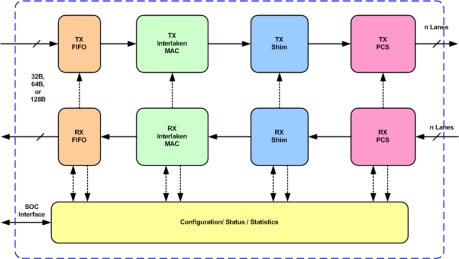

Interlaken Controller

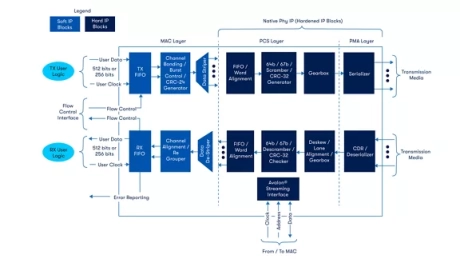

- MAC layer with fast AMBA CXS interface

- PCS layer highly configurable with up to 48 lanes

- Multi-lane configurations, up to 48 lanes

- 64B 67B encoding/decoding supported

-

Interlaken Core (Up to 600G)

- Support for up to 600 Gbps of throughput

- Data striping and de-striping across 1 to 24 lanes

- Programmable BurstMax, BurstMin, BurstShort and MetaFrameSize parameters

- Support for Synchronization, Scrambler State, Diagnostic, and Skip Word Block Types

-

UltraScale / UltraScale+ Interlaken

- The lane logic only mode allows each serial transceiver to be used to build a fully featured Interlaken interface. In devices with 48 serial transceivers, up to 600 Gb/s of total throughput can be sustained.

- The protocol logic supported in each integrated IP core scales up to 150 Gb/s. The Interlaken integrated IP core solution is designed to be compliant with Interlaken Protocol Definition, Revision 1.2, October 7, 2008.

- The integrated IP core implements both the lane logic and protocol logic portions of the specification, which saves approximately 60k+ System Logic Cells per instantiation and uses about 1/8th the power of equivalent soft implementations.