eMMC 5.0 IP

Filter

Compare

48

IP

from

10

vendors

(1

-

10)

-

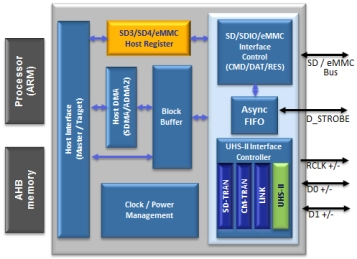

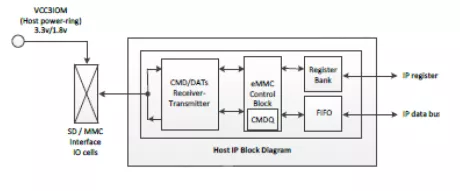

SD 4.1 / SDIO 4.1 / eMMC 4.51 Host Controller IP

- The SD 4.1/SDIO 4.1 IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies.

- SD 4.1 Host Controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds.

-

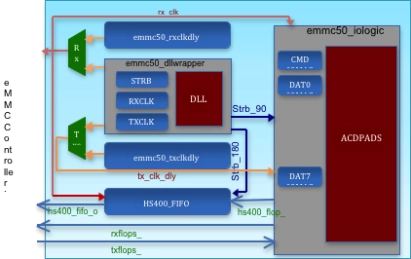

eMMC 5.1 HS400 PHY

- The eMMC5.1 PHY is a fully compliant PHY layer for JEDEC eMMC5.1 and eMMC5.1 JESD84-B50 specification. It is backward compatible with eMMC4.51 and earlier versions of the specifications.

- This allows the designers of the SoC to easily support the eMMC interface and optimize the performance and power while maintaining interoperability with eMMC 5.0 and eMMC 5.1 devices.

-

SD 4.1 eMMC 5.1 Dual Host Controller IP

- The SD 4.1/SDIO 4.0/eMMC 5.0 Host IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD 4.1 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the SD 4.1 / eMMC5.1 Host IP.

- eMMC 5.1 is backward compatible to the previous versions.

-

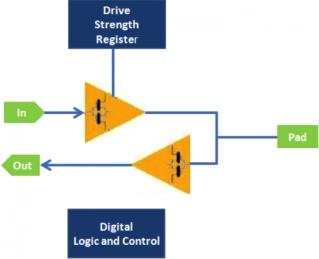

eMMC 5.1 Device I/O Pad

- The eMMC 5.1 Device I/O is verified to be fully compliant I/O interface for JEDEC eMMC 5.1 when rectified and eMMC 5.0 JESD84-B50 specification. It is backward compliant with eMMC4.51 and earlier versions of the specifications.

- This allows the designers of the SoC to easily support the EMMC interface and optimize the performance and power while maintaining interoperability with eMMC 5.0 and eMMC 5.1 hosts.

-

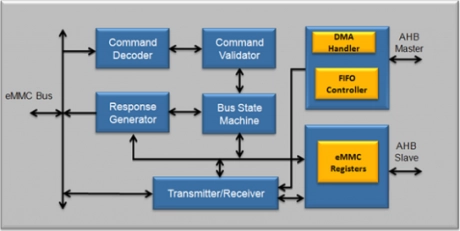

eMMC 5.1 Device Controller IP

- The eMMC 5.1 Device Controller IP is compliant with the latest eMMC specification. The controller provides a bandwidth of up to 3.2 Gb/s (400MB/s) in HS400 DDR mode running with a 200 MHz clock.

- A NAND Flash controller can be connected to the eMMC controller. In such an implementation, the controller’s AHB interface provides a channel for data transfers between the eMMC device controller and a NAND flash controller (also available from Arasan).

-

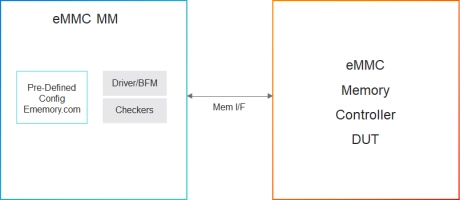

Simulation VIP for eMMC

- High speed modes

- 200 MB/s Read and Write operation. HS400 Dual Data Rate Read and Write interface

- General eMMC Functionality

- 48-bit input command format and R1, R1b, R2 response formats

-

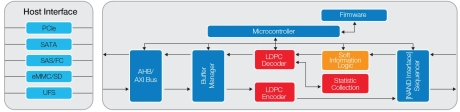

eMMC LDPC Encoder/Decoder

- Supports data rates from 50 MB/s to 9.0 GB/s.

- Enables custom LDPC core development for specific requirements.

- Wide range of codeword sizes.

- Maximum supported parity.

-

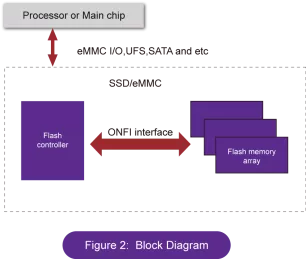

ONFI 5.0 PHY IP

- Compliant with ONFI 5.0 specification

- Supports NV-DDR2 mode

- Supports NV-DDR3, NV-LPDDR4, with a maximum rate of 2400MT/s

- Supports PHY Independent TX/RX Training mode

-

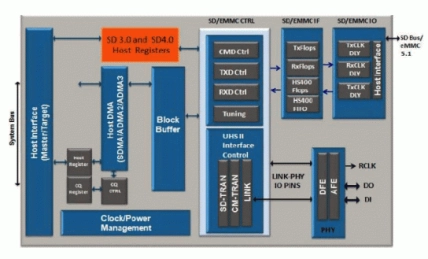

SD 5.1 / eMMC 5.1 Host Controller IP

- SD IP Features :

- Support SD system specification version 5.1

- Support Application Performance Class 1.

- Backward compatible to SD2.0 host

-

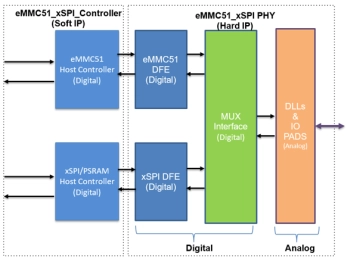

xSPI + eMMC Combo PHY IP

- This IP integrates both xSPI (Expanded Serial Peripheral Interface) and eMMC 5.1 PHY (Physical Layer) into a single unified solution, enabling support for two distinct memory protocols within the same IP.

- By combining the PHY layers for both interfaces, the design simplifies system integration, reduces area and pin count, and enhances design flexibility for SoCs that require both boot and high-speed storage functionality.