analog front-end IP

Filter

Compare

182

IP

from

29

vendors

(1

-

10)

-

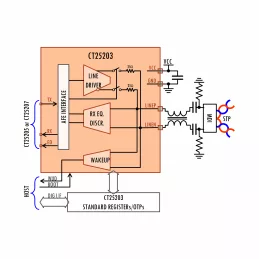

IEEE 802.3cg® 10BASE-T1S Analog Front-End

- Single min 3.3V supply

- Low Power consumption meeting OPEN Alliance TC10 requirement in sleep mode

- OPEN Alliance TC10 Wake Up detection

- Voltage and current references, test infrastructures, included

- Supply regulators, 25MHz XTAL and x4 (100MHz) DLL available upon request in the target silicon process.

-

TSMC CLN12FFC 500MHz Analog Front-End

- TSMC 12 nm 0.8 V/1.8 V CMOS LOGIC FinFET Compact Process

- Metal scheme: 1P9M (2Xa1Xd_h_3Xe_vhv_2Z) + UT-ALRDL

- Operating junction temperature: -40 °C ~ 125 °C

- 2-ch 12 bit 250 MHz SAR ADC

-

TSMC CLN28HPC ABB Analog Front-End

- TSMC 28nm CMOS High Performance Compact Mobile Computing (HPC) process

- Metal Scheme: 5X2Z (1P8M)

- 1.8V analog and 0.9V digital supply voltage

- Five channel IQ-ADCs with analog filters

-

TSMC CLN12FFC 16Gsps Analog Front-End

- TSMC 12 nm 0.8 V/1.8 V CMOS LOGIC FinFET Compact Process

- Metal scheme: 1P9M (2Xa1Xd_h_3Xe_vhv_2Z) + UT-ALRDL

- Operating junction temperature: -40 oC ~ 125 oC

- Support 4T4R

-

TSMC CLN28HPC+ 2.4GSps Analog Front-End

- 1.8V analog and 0.9V digital supply voltage

- Power consumption (ADC macro): 730mW (typical)

- Power consumption (DAC macro): 220mW (typical)

- Maximum sampling rate: 2.4GSps

-

ONFI 3.0 Compatible I/O Buffer on TSMC CLN28HPL

- High speed, source synchronous, bi-directional I/O buffer supporting the Open NAND Flash Interface (ONFI) 3.0 standard

- Operation up to 200MHz DDR (400Mbps) performance with single load topology

- Designed with core and 1.8V IO oxide devices

- Built-in ODT (On-Die Termination)

-

DDR3/DDR3L Compatible I/O Buffer on TSMC CLN40G

- High-Speed Bi-directional DDR3/DDR3L compatible I/O buffer

- Operation up to 1066MHz DDR (2133Mbps) performance with single load topology

- Designed with core and 1.8V IO oxide devices

- Built-in ODT (On-Die Termination)

-

Complete measurement analog front end (AFE) IP for single phase power metering

- Embedded Computation Engine for utility billing applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

Complete measurement analog front end (AFE) IP for single phase power metering

- Embedded Computation Engine for utility billing applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

Complete measurement analog front end (AFE) IP for three-phase power metering

- Embedded Computation Engine for utility biling applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise