Wireless LAN IP

Filter

Compare

16

IP

from

11

vendors

(1

-

10)

-

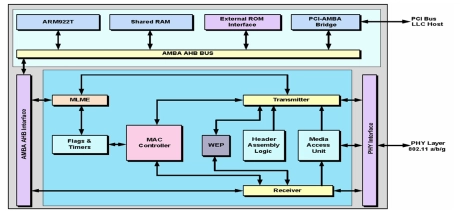

802.11 a b and g IEEE Standard - Wireless LAN

- The MAC core for Wireless LAN is compatible with 802.11 a b and g IEEE Standards.

- It is designed to handle packetized DSSS (Direct Sequence Spread Spectrum) and OFDM (Orthogonal Frequency Division Multiplexing) data transmissions; the software implementation supports all data rates.

- The MAC management or control functionality is implemented in firmware while the time critical functionality is implemented in hardware.

-

WiGig Wireless Display Codec

- WDE / WiGig H.264 Codec IP

- WiGig H.264 codec IP is designed to be integrated into a WiGig device, providing:

- * high-performance high-quality H.264 video compression,

- High 4:4:4 Intra Profile, support 8/10/12 bits

-

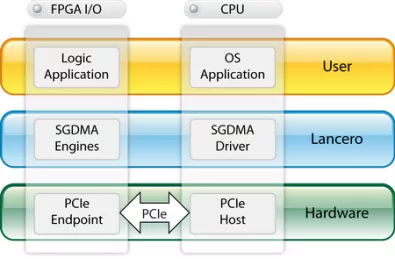

Lancero Scatter-Gather DMA Engine for PCI Express

- PCIe I/O performance: 200 MB/s x1 Gen 1 up to 3360 MB/s x8 Gen 2

- Easily connect logic and high-speed I/O peripherals to PCI Express

- Target Bridge supports Avalon Memory Mapped custom logic

- SGDMA Engine supports Avalon Streaming burst access devices

-

60 GHz Power Amplifier

- Frequency Range: 57 -64 GHz

- High Output Power: P1dB = 14.5 dBm @ f = 61.5 GHz

- High Efficiency: PAE = 20 %

- High Linear Gain: │S21│ = 20 dB @ f = 61.5 GHz

-

60GHz Low Noise Amplifier

- Frequency Range: 57 -64 GHz

- Noise figure = 6.7 dB @ f = 61.5 GHz High Linear Gain: │S21│ = 20 dB @ f = 61.5 GHz

- Supply Voltage: 2.7 – 3.3 V

-

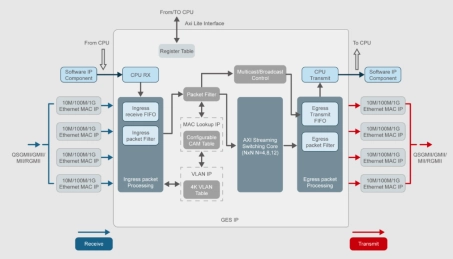

Lithe Layer 2 Gigabit Ethernet Switching IP

- The Lithe Layer 2 Gigabit Ethernet Switching IP is a comprehensive solution for building scalable and efficient network infrastructures.

- Designed to operate at the data link layer of the OSI model, our Lithe Layer 2 IP offers advanced networking capabilities for local area networks (LANs), metropolitan area networks (MANs), and wide area networks (WANs).

- With support for various networking protocols and features, our Lithe IP enables seamless connectivity, reliable data transmission, and efficient network management.

-

Reed-Solomon Decoder

- Flexible RS Decoder meeting the requirements of most standards that employ RS codes including: IEEE 802.16, DVB-x, G.709, ETSI-BRAN, and CCSDS

- Fully synchronous design using a single clock

- Supports continuous input data with no gap between code blocks

- Supports symbol size from 3 to 12 bits and any primitive field polynomial for a given symbol width

-

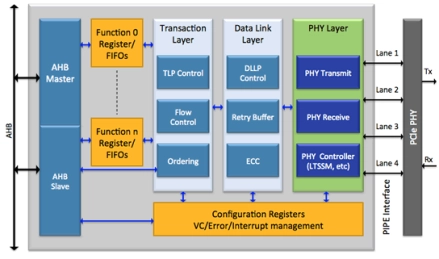

PCIe End Point IP Core

- The PCI Express End Point is a high-speed, high-performance, and low-power IP core that is fully compliant to the PCI Express Specification 1.1 and 2.0.

- The IP core is designed for applications in computing, networking, storage, servers, wireless, and consumer electronics.

-

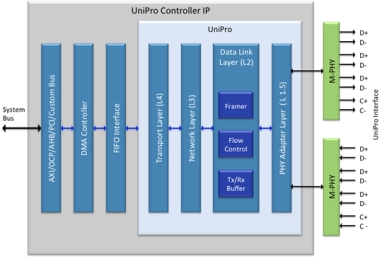

UniPro℠ Controller IP Core

- The UniPro Controller IP core is fully compliant with the UniPro specification version 1.6 and supports the physical adapter layer of the M-PHY® specification.

- MIPI UniPro is a high-performance, chip-to-chip, serial interconnect bus for mobile applications. Designed to support up to 5Gbps per data lane, it is scalable from one to four bidirectional lanes.

-

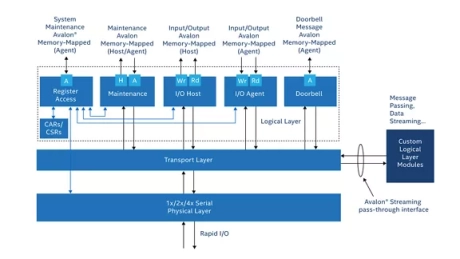

RapidIO Intel® FPGA IP

- Intel is discontinuing the intellectual property (IP) for RapidIO I and RapidIO II, more information can be found in the product discontinuance notification (PDN2025).