VGA IP

Filter

Compare

61

IP

from

21

vendors

(1

-

10)

-

VGA with gain 0.5 to 128 - TowerJazz 0.18um

- Area: 0.356mm2

- Idd (Current consumption): 5mA

- gainmax (Maximum gain): 128

- THD (Total harmonic distorsion): 70dB

-

VGA/LCD Display Controller

- Resolutions of up to 2048x2048 @ 60Hz in ASIC. Higher resolutions are possible, depending on silicon process

- Resolutions of up to 1024x1024 @ 60Hz in FPGA. Higher resolutions are possible, depending on FPGA speed grade

- 32 bits per pixel (bpp), 24bpp and 16bpp color modes

- 8bpp grayscale and 8bpp pseudo-color modes

-

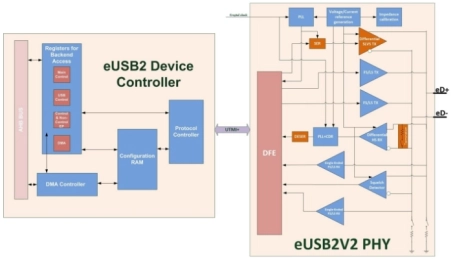

Embedded USB2 (eUSB) Controller + PHY IP

- Compliant to Embedded USB2 Version2.0, Aug 2024

- Supports high-speed, full-speed, and low-speed operation.

- Meet low voltage requirement (1.0V – 1.2V)

- No change in existing USB2/USB3 Port

- Supports symmetric and asymmetric data rates

-

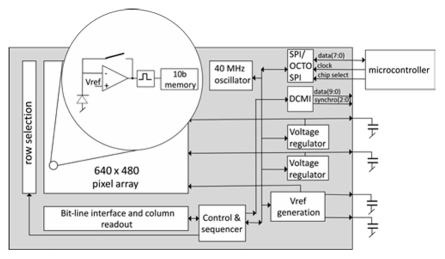

Ultra-low power high dynamic range image sensor

- Resolution: VGA (640 x 480)

- Backside illuminated sensor

- Pixel size: 6.3 μm x 6.3 μm

- Fill factor: 83 %

- Dynamic range: 120 dB intra-scene

-

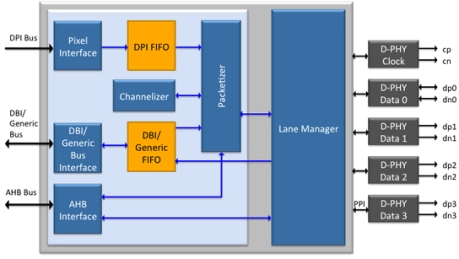

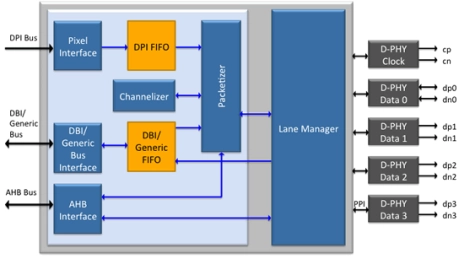

DSI v1.3 Transmit IP Core

- The DSI Tx Controller IP is designed to provide MIPI DSI 1.3 – compliant high-speed serial connectivity for the host (mobile application processor) using 1 to 4 D-PHYs depending on bandwidth needs.

-

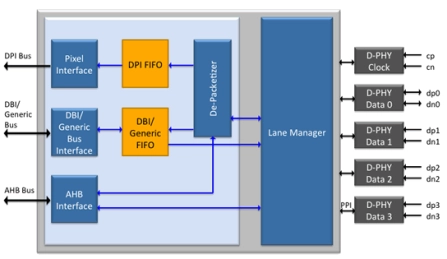

DSI Receiver Controller

- The DSI v1.3 Receiver Controller IP is designed to provide MIPI DSI 1.3 compliant high-speed serial connectivity for device (mobile display modules) with Type 1 to 4 architectures.

- Serial connectivity to the mobile applications processor’s DSI host is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs.

-

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

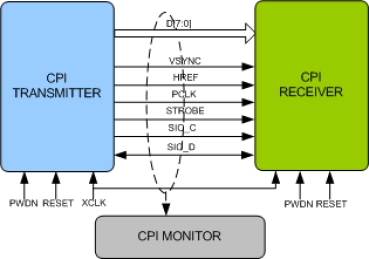

Camera Parallel Interface (CPI) Verification IP

- Full CPI transmitter device and receiver device functionality.

- Supports packing of all the video formats supported by the CPI OV7670 v1.0.

- Supports RGB444,RGB555,RGB565 color format.

- Supports Device control register set as per CPI OV7670 v1.0.

-

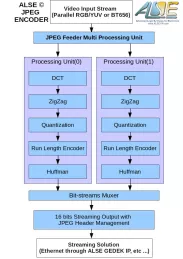

High-Speed JPEG Video Encoder

- Speed and Area-Optimized encoder engine suitable for both still image and real-time video compression.

- 8 bits (byte) Streaming output interface with Backpressure. Easy to connect to the ALSE Ethernet communication engine for example. Output format is 8x8 YUV Blocks (4:2:2).

- Supports any image resolution up to 64k x 64k.

- Suitable for still image and real-time video (streaming).