USB 2.0 HS OTG PHY IP

Filter

Compare

30

IP

from

12

vendors

(1

-

10)

-

USB 2.0 HS PHY Interface

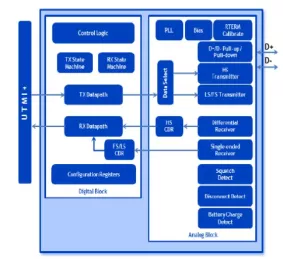

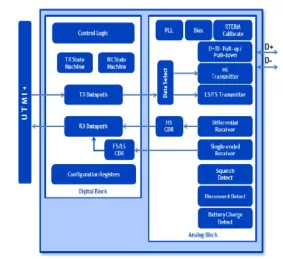

- The USB PHY IP is UTMI interface compatible and a dedicated circuit for full-function USB 2.0 transceivers.

- It is a mixed-signal circuit, with the analog part including the transmitting and receiving circuits, level conversion circuits, bus driver circuits, etc., and the digital part including the transmitting and receiving and speed switching control circuits, encoding and decoding circuits, serial-to-parallel and parallel-to-serial conversion circuits, as well as digital CDR circuits, etc.

-

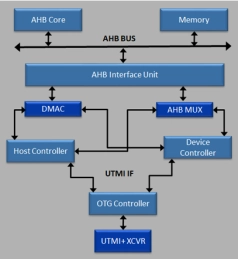

USB 2.0 OTG Dual Role Device (DRD) Controller

- Compliant with OTG Supplement Rev. 1.0a

- USB 2.0 Compliant

- Supports 480 Mbit/s (HS), 12 Mbit/s (FS), and 1.5 Mbit/s (LS)

- Supports Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

-

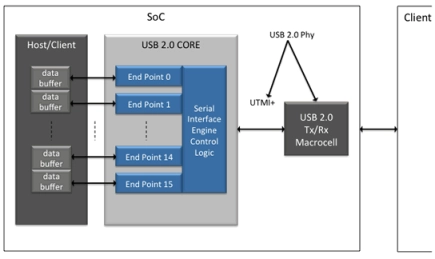

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

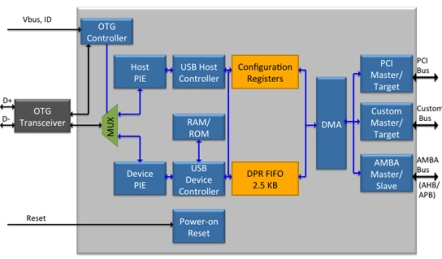

USB 2.0 OTG IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

USB 2.0 PHY

- ? 480-Mbps high-speed, 12-Mbps full-speed, and 1.5-Mbps low-speed serial (Host mode only) data transmission rates

- ? Supports high-speed power modes: suspend, resume, and remote wakeup.

- ? USB 2.0 test modes

- ? 45-? termination, 1.5-k? pull-up and 15-k? pull-down resistors with support for independent control of the pull-down resistors

-

USB 2.0 PHY IP, Silicon Proven in SMIC 40LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in SMIC 55LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 PHY IP, Silicon Proven in SMIC 14SF+

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 2.0 Hi-Speed OTG Controller version 4 with Active Clock Gating to save active power

- Configuration options to maximize performance and minimize CPU interrupts

- Flexible parameters enable easy integration into low and high-latency systems

- Transfer- or transaction-based processing of USB data based on system requirements

- Configurable data buffering options to fine-tune performance/ area trade-offs