Sub-LVDS IP

Filter

Compare

45

IP

from

12

vendors

(1

-

10)

-

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

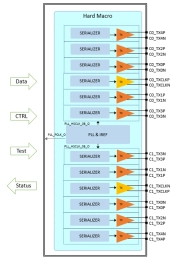

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

subLVDS IO Pad Set

- ? Powered from 1.8V ±10% and 1.1V to 1.2V (±10%) core power supplies

- ? Operates up to 700 MHz (1400Mbps)

- ? Input receive sensitivity of 50mV peak differential (without hysteresis)

- ? Common mode range from 0.4V to 1.4V (limited by Power Supply)

-

subLVDS I/O Pad Set

- Input receive sensitivity of 50mV peak differential (without hysteresis)

- Common mode range from 0.4V to 1.6V (limited by Power Supply)

- Powered by 1.8V I/O and 1.1V core supplies

- Power consumption: 3.4 mW max @ 800 MHz

-

subLVDS IO Pad Set

- Input receive sensitivity of 50mV peak differential (without hysteresis)

- Common mode range from 0.4V to 1.8V (limited by power supply)

- Powered by 1.8V I/O and 1.1V core supplies

- Power consumption: 4.94 mW max @ 600 MHz

-

subLVDS IO Pad Set

- Powered from 1.8V ±10% and 1.0V(±10%) to 1.1V(-10%/+5%) core power supplies

- Operates up to 1GHz (2Gbps)

- Input receive sensitivity of 50mV peak differential (without hysteresis)

- Common mode range from 0.4V to 1.4V (limited by Power Supply)

-

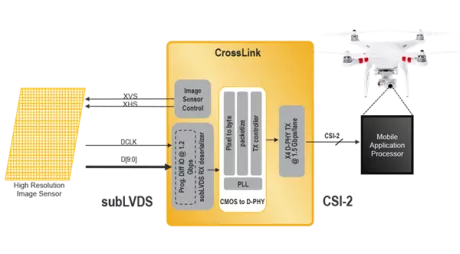

SubLVDS to MIPI CSI-2 Image Sensor Bridge

- Supports 4, 8, or 10 data lanes from Sony image sensor in 10-bit or 12-bit pixel widths

- Interfaces to MIPI CSI-2 Devices with 1 clock lane and 4 data lanes up to 6 Gbps total bandwidth

- Generates XVS & XHS for image sensors in slave mode operation

- Handles Sony IMX SubLVDS image sensors such as IMX236, IMX172, IMX178, IMX226, etc.

-

SMIC 55nm sub-LVDS Receiver

- Supports Aptina HiSPi, Panasonic LVDS, or Sony LVDS parallel input signal

- 10 data channels / 2 clock channel integrated

- Maximum serial data rate per channel: 1Gbps

- Supports up to 20-bit CMOS parallel input (DVP input mode)

-

SMIC 55nm sub-LVDS Receiver

- Supports Aptina HiSPi, Panasonic LVDS, or Sony LVDS parallel input signal

- 8 data channels / 2 clock channel integrated

- Maximum serial data rate per channel: 1Gbps

- Supports up to 16-bit CMOS parallel input (DVP input mode)

-

GLOBALFOUNDRIES 28nm SLP sub-LVDS Receiver

- Supports Aptina HiSPi, Panasonic LVDS, or Sony LVDS parallel input signal

- 4 data channels / 1 clock channel integrated

- Maximum serial data rate per channel: 1Gbps

- Supports up to 8-bit CMOS parallel input (DVP input mode)