Sidense OTP IP

Filter

Compare

3

IP

from

3

vendors

(1

-

3)

-

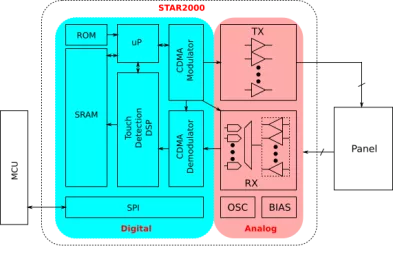

Large screen capacitive touch panel controller

- Projected-capacitive touch panel controller ASIC

- Proprietary CDMA-based TX/RX architecture

- For certain panels with very high drive attenuation optional high voltage drive in HV process is available

- Single chip supports 17” display: 60 driven lines (TX), 80 sensed lines (RX)

-

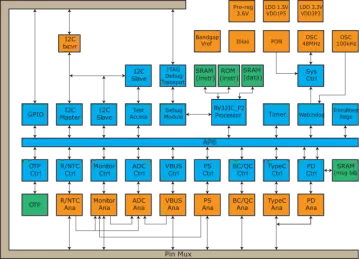

Digital and mixed-signal IP and ASIC RISC-V reference design for USB Type-C/PD power adapter/charger

- RISC-V RV32EC processor subsystem with debug module, JTAG debug transport, and instruction and data ROM and SRAMs