SD SDIO Combo Device IP

Filter

Compare

7

IP

from

7

vendors

(1

-

7)

-

SD Card / SDIO Card Combo Device IP

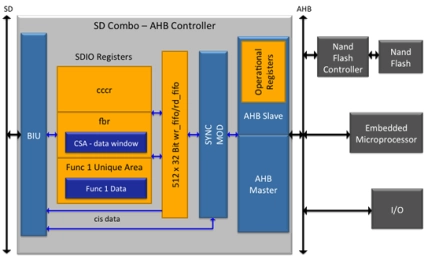

- SD / SDIO Card Combo Device IP core is SD memory controller and a SDIO controller with an AHB interface.

- Combining with the optional NAND Flash Controller IP, the SD/SDIO Combo Device IP provides an integrated SD memory Card solution for designs that utilize NAND flash memory.

-

Simulation VIP for SD CARD and SDIO

- SD Card device standard

- Speed Range A and B

- Default Speed Range A and faster Range B support

- PHY-LINK I/F

-

eMMC/SD/SDIO Combo IP

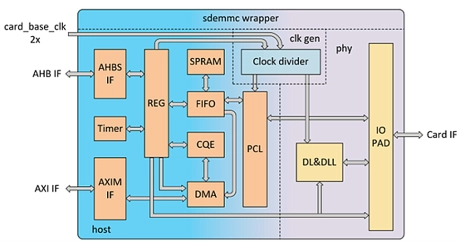

- The eMMC/SD/SDIO Combo IP is a comprehensive solution designed to support high-performance storage and I/O connectivity for a wide range of applications

- This IP integrates a host controller and PHY, enabling seamless communication with eMMC, SD, and SDIO devices

- When connecting the SD/SDIO device, the IP supports DS, HS, SDR12, SDR25, SDR50, SDR104, and DDR50 speed modes

-

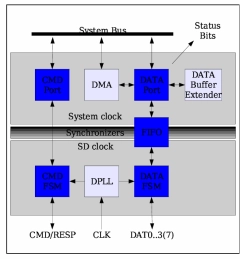

SD/SDIO Device IP Core

- A compact low power and scalable IP core which provides a simple, firmware-friendly cost-effective Physical Link interface for memory, i/o and combo devices, such as SD-based memory cards, Mini SD, Micro SD, SDIO Bluetooth devices, SDIO GPS, etc.

- The SD/SDIO Device IP core is designed for an easy integration with any card controller and any system bus, with minimum firmware development overhead.

-

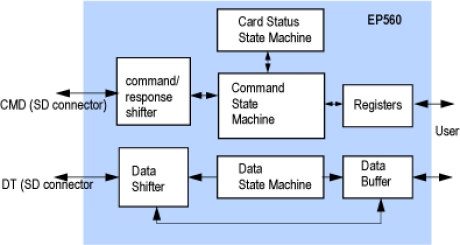

SDIO/SD Memory/MMC Slave Controller

- Compatible with SD/SDIO specification 2.0 with 1 and 4 bit data transfer.

- Provides SD interface to peripheral or memory device through a simple address/data interface.

- Support SD, SPI and optional MMC bus protocol.

- Support for both standard capacity and high capacity (SDHC) memory cards.

-

I/O Library

- Supports process nodes from 0.13um to 3nm

- ESD protection: Robust ESD protection mechanisms ensuring device reliability and longevity

- Temperature Range: Designed for wide operational temperature ranges, suitable for consumer, AI to automotive applications

- Signal Integrity: Optimized for low noise and high signal integrity, ensuring reliable data transmission across all interfaces