SATA 3.0 Controller IP

Filter

Compare

20

IP

from

13

vendors

(1

-

10)

-

-

SATA HOST CONTROLLER IIP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

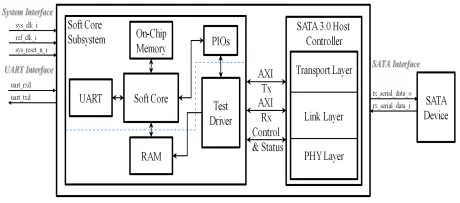

SATA 3 Controller IP

- Simple AXI streaming TX and RX interface for application layer communication.

- It supports Native Command Queuing and key primitives/FIS types from SATA specifications.

- Compliant with Serial ATA 3.0 specification.

- Supports data rates of 1.5/3/6 Gbit/s.

-

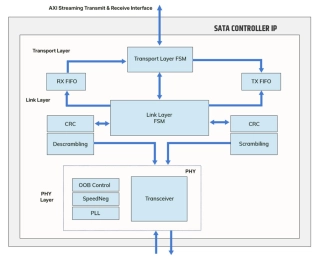

SATA HOST Controller

- Designed to SATA v3.0 (6Gbps)

- Low Latency: 66K IOPS Read, 67K IOPS Write (4k blocks)

- Connects to SAPIS compliant serial ATA Phy

- Manage SATA reference frequency difference between the FPGA and the Disk

-

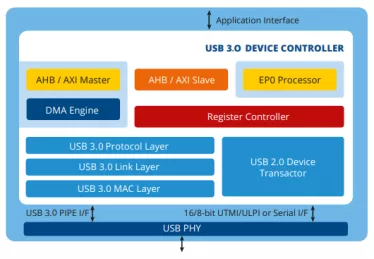

USB 3.0 Gen1 / Gen2 Device Controller IP

- USB 3.0 Device controller can be configured to support all types of USB transfers – bulk, interrupt and isochronous.

- Allows dynamic configuration to support configurable number of endpoints, interfaces, alternate interfaces and configurations.

- USB 3.0 Device controller can be configured to support any combinations of USB 3.0 interface speeds – SSP (10 Gbps), SS (5 Gbps), HS (480 Mbps), FS (12 Mbps) and LS (1.5 Mbps). Sample combinations are SSP & SS only, SSP & SS & HS only, SSP & SS & HS & FS only, SS only, SS & HS only, SS & HS or FS only.

- USB 3.0 Device controller has full support for all low power features of the USB specification supporting suspend and remote wakeup, USB 3.0 low power states – U1/U2/U3 and USB 2.0 Link Power Management states – L1, L2.

-

Serial ATA I/II/III Host Controller IP Core Compliance Certified by UNH Labs

- High Throughput

- Low Latency

- Connects to SAPIS compliant serial ATA Phy

-

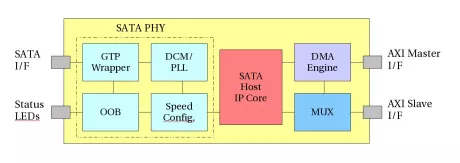

SATA-III Host Controller

- Fully compliant with the Serial ATA specification revision 2.6

- Simple transaction interface with Host processor and DMA Engine

- 32-bit internal data path

- 8KB FIFO implemented by BlockRAM in both transmit and receive paths

-

SATA-II Host Controller Core

- Fully compliant with the Serial ATA specification revision 2.6

- Simple transaction interface with Host processor and DMA Engine

- 32-bit internal data path

- 8KB FIFO implemented by BlockRAM in both transmit and receive paths

-

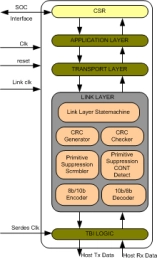

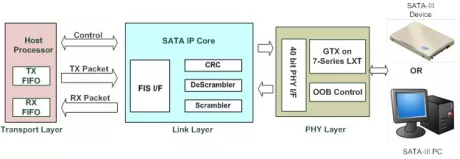

SATA-IP core - File system management without CPU

- SATA IP core compliant with the Serial ATA specification revision 3.0 and work on AMD UltraScale and 7-Series device.

- This IP core provide link layer. Design Gateway provide transport layer and 150MHz GTX physical layer design for 6.0Gbps SATA-III interface as reference design.

- It can connect with SATA-III HDD directly without external PHY chip.

-

SATA RAID Core

- Hardware-only RAID; Firmware is not needed

- Can work for 2n number of drives

- Supports RAID Level 0

- Supports 1.5, 3.0 and 6.0 GHz speed