RegEx IP

Filter

Compare

17

IP

from

10

vendors

(1

-

10)

-

100G OTN Regenerator/Repeater(OTL4.4)

- 200MHz+ push button core performance.

- All products designed from ground up to allow future datapath & channel scaling.

- Softcore Microprocessor subsystem connected to generic core registers.

- OTL4.4 client & line interface.

-

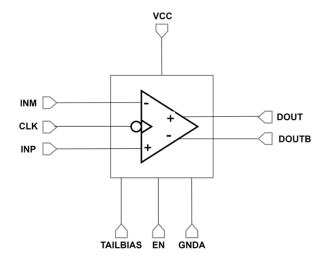

Voltage Latched Comparator

- A high-speed voltage clocked comparator with rail- to-rail outputs and no hysteresis.

- The typical propagation delay is 19ns while applying a differential input signal of 1mV over the offset voltage.

- The comparator operates with a supply voltage of 3.3V typical (VCC).

-

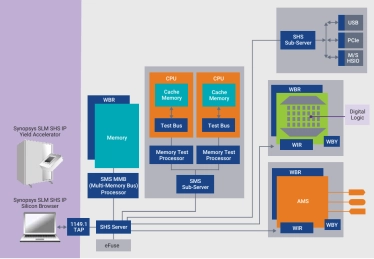

SLM SHS IP

- The SLM SHS IP is an automated hierarchical test solution for efficiently testing SoCs or designs using multiple IP/cores, including analog/mixed-signal IP, digital logic cores and interface IP.

- It significantly reduces test integration time by automatically creating a hierarchical IEEE 1500 network to access and control all IP/cores at the SoC level, and increases test quality of results (QoR), including optimizing test time and power through flexible test scheduling of IP and cores.

-

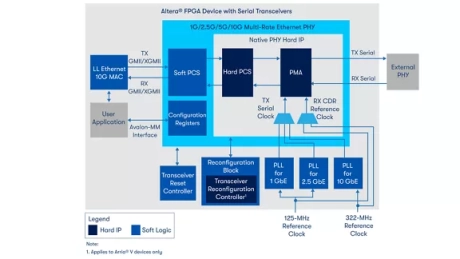

Multi-Rate Ethernet PHY FPGA IP

- The Multi-Rate Ethernet PHY FPGA IP core can dynamically support multiple data rates without any design regeneration or device reconfiguration

- This IP allows the creation of a 1G to 10G configuration that allows dynamic reconfiguration across all Ethernet rates from 10M, 100M, 1G, 2.5G, 5G, and 10G.

-

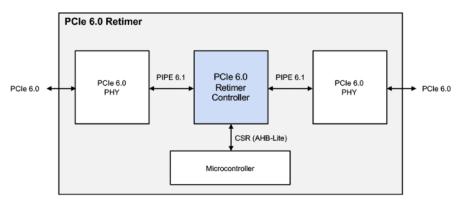

PCIe 6.0 Retimer Controller with CXL Support

- Designed to the latest PCI Express 6.0 (64 GT/s), and capable of supporting 32.0, 16.0, 8.0, 5.0 and 2.5 GT/s link rates

- Supports x1, x2, x4, x8 and x16 link widths

- CXL aware and supports sync header bypass

- Supports PIPE 5.2/6.1 compatible PHYs

- Optimized data-path for low latency insertion

-

Multi-LEO Satellite Link Emulator

- Multi-LEO Simulation

- Dynamic Channel Modelling

- Flexible Configuration

- Scalability

-

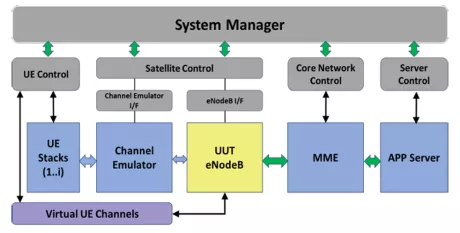

NTN eNodeB System Test Bench

- Allows end-to-end testing of NB-IoT NTN system in lab environment.

- supports 3GPP® Release 17 and 18 standards.

- supports LEO transparent or regenerative modes of operation.

- multiple-instancing and virtualisation to simulate UE community.

-

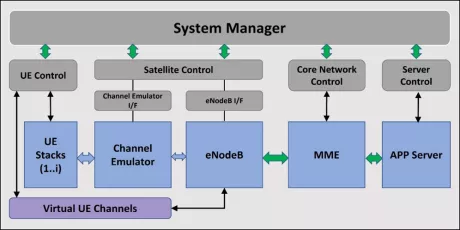

NTN System Test Bench

- Allows end-to-end testing of NB-IoT NTN system in lab environment.

- supports 3GPP® Release 17 and 18 standards.

- supports LEO transparent or regenerative modes of operation.

- multiple-instancing and virtualisation to simulate UE community.

-

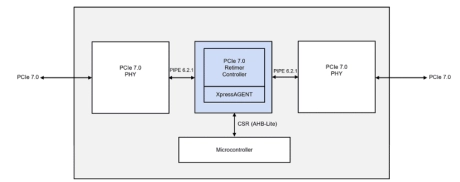

PCIe 7.0 Retimer Controller with CXL Support

- Supports PCIe 7.0 128 GT/s speeds at up to x16 lanes

- CXL 3.0 aware

- Supports PIPE 6.2.1 compatible PHYs

- Optimized for low latency

- Highly-configurable equalization algorithms and adaptive behaviors

-

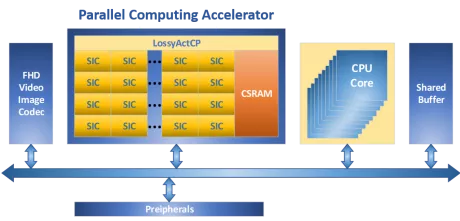

Low-power high-speed reconfigurable processor to accelerate AI everywhere.

- Multi-Core Number: 4

- Performance (INT8, 600MHz): 0.6TOPS

- Achievable Clock Speed (MHz): 600 (28nm)

- Synthesis Logic Gates (MGates): 2