RapidIO IP

Filter

Compare

25

IP

from

12

vendors

(1

-

10)

-

Serial RapidIO IP Core

- Serial RapidIO is a communication protocol developed to ensure fast and reliable interconnection between the vendor's boards.

- The basic idea behind Serial RapidIO is to enable communication speeds up to 25Gbps/lane (up to 100Gbps/port with a 4-lane port) while allowing the user to send a variety of different message s with CRC protection, retransmission on error, and virtual channels for quality of service.

-

RapidIO Intel® FPGA IP

- Intel is discontinuing the intellectual property (IP) for RapidIO I and RapidIO II, more information can be found in the product discontinuance notification (PDN2025).

-

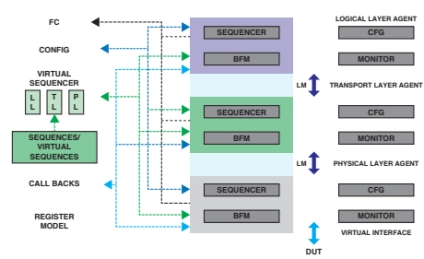

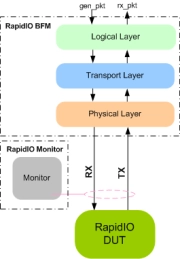

RapidIO Verification IP (VIP)

- The RapidIO Verification IP (VIP) provides highly capable compliance verification solution for the RapidIO protocol.

- The RapidIO VIP is system Verilog (SV) based and supports standard Universal Verification Methodology (UVM).

- It can be easily combined with any other UVM compliant verification components to extend a broader verification environment.

-

RapidIO Verification IP

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 8b/10b and 64b/67b Encode and Decode functions.

- Supports scrambler/Descrambler.

-

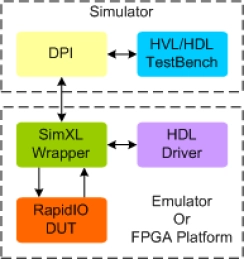

RapidIO Synthesizable Transactor

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 25.78125Gbaud/s, 12.5Gbaud/s, 10.3125Gbaud/s, 6.25Gbaud/s, 5Gbaud/s,3.125 Gbaud/s, 2.5 Gbaud/s, 1.25 Gbaud/s.

- 8b/10b Encode and Decode functions.

-

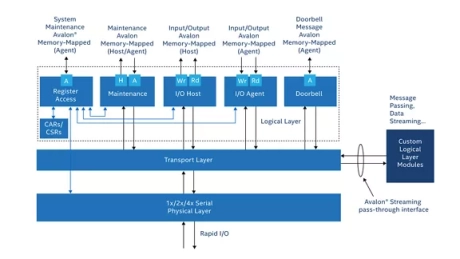

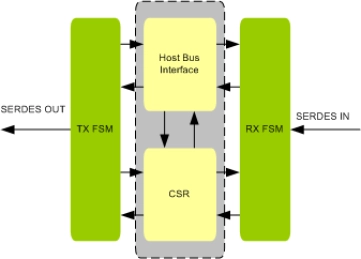

RAPIDIO EndPoint Controller IIP

- Compliant with RapidIO Interconnect 2.2 specification

- Supports all Capability Registers(CARs) and Configuration and Status Registers(CSRs)

- Supports high link utilization and low latency

- Supports efficient receive and transmit buffering scheme

-

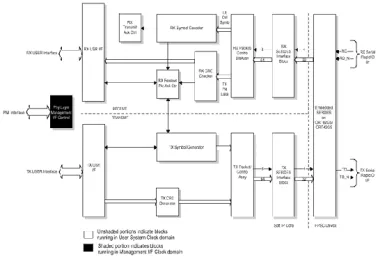

Serial RapidIO 2.1 Endpoint IP Core

- LatticeECP3 AMC Evaluation board

- Associated cables

- AMC interface card

- Demonstration bitstreams and files

-

Serial RapidIO - Physical Layer Interface

- Supports High Speed 1x Mode (up to 2.5 Gbps)

- 8B/10B Encoding and Decoding

- Clock and Data Recovery (CDR)

- Lane Synchronization

-

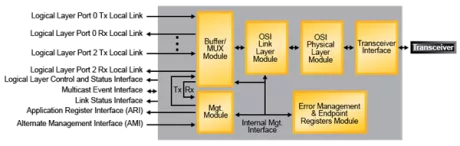

LogiCORE IP Serial RapidIO Gen 2

- 1x, 2x, & 4x Serial PHY - supports Artix-7, Kintex-7, Zynq-7000, Virtex-7, and Virtex-6 FPGAs

- 1x, 2x & 4x Serial PHY - supports 1.25, 2.5, 3.125, 5.0, and 6.25 Gbps line speed

- Supports IDLE1 and IDLE2 sequence

- Supports Packet Retry, stomp, transmission error recovery, throttle-based flow control and CRC

-

Serial RapidIO LogiCORE IP

- 1x & 4x Serial PHY - Supports Virtex-6 LXT/SXT/HXT, Spartan-6 LXT, Virtex-5 LXT/SXT/FXT, and Virtex-4 FX FPGAs

- 1x & 4x Serial PHY - Supports 1.25, 2.5, 3.125, 5.0 Gpbs line speed

- 1x & 4x Serial PHY - 64-bit internal data path

- Supports Packet Retry, stomp, transmission error recovery, throttle-based flow control and CRC