PCIe Gen4 IP

Filter

Compare

52

IP

from

21

vendors

(1

-

10)

-

Low Power 1-22G PCIe Gen4 / SAS4 PHY on TSMC CLN16FFC

- Industry leading low power PMA macro – 184mW per lane at 22.5Gbps (8.2mW/Gbps) and 108mW per lane at 16Gbps (6.75mW/Gbps), inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.145 mm2 total active area per lane

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

- Multi-orientation macros of 4, 8 and 16 lane SERDES are available for most common metal stacks

-

PCIe Gen4 PHY, x1-lane, RC/EP, TSMC 16FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x4-lane, RC/EP, TSMC 16FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x1-lane, RC/EP, TSMC 12FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x4-lane, RC/EP, TSMC 12FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x2-lane, RC/EP, TSMC N7, 1.8V, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x2-lane, RC/EP, TSMC N6, 1.8V, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

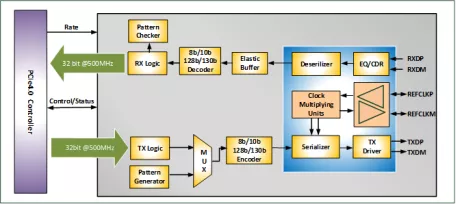

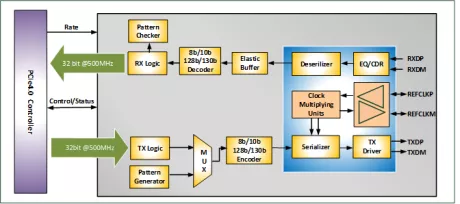

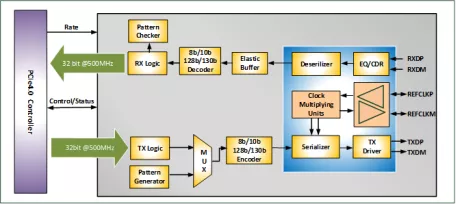

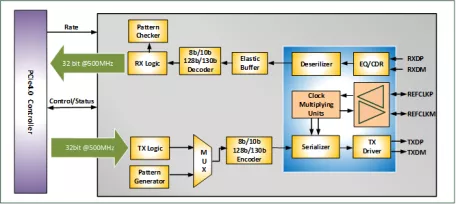

PCIe Gen4 RX/TX IP Supporingt PCIe 1.0/2.0/3.0/4.0 up to 16Gbps. CTLE boosts up to 18dB at 8GHz

- Support PCIe 1.0/2.0/3.0/4.0 up to 16Gbps. CTLE boosts up to 18dB at 8GHz

-

PCI Express Gen 4 PHY

- Support 16GT 8GT 5GT 2.5GT data rate

- Compliant with PCI Express 4.0, 3.1, 2.1, 1.1 and PIPE 4.2 standards

- x1, x2, x4, x8, x16 lane configuration with bifurcation

- Multi-tap adaptive programmable continuous time linear equalizer (CTLE) and decision feedback equalizer (DFE)