Northwest Logic IP

Filter

Compare

5,396

IP

from

212

vendors

(1

-

10)

-

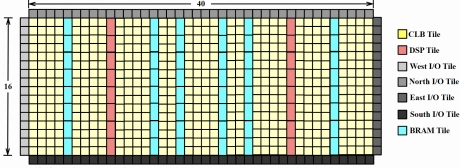

eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- RapidFlex eFPGA IP provides a reconfigurable, upgradeable, and iterative logic computing layer for SoCs, MCUs, AI accelerators, industrial control, and communication chips.

- Based on RapidFlex's self-developed ArkAngel® toolchain (AAEE), our eFPGA core delivers full-flow capabilities from architecture exploration → RTL → physical implementation (GDSII) → digital design flow verification, leading the industry in performance density, integrability, and toolchain experience.

-

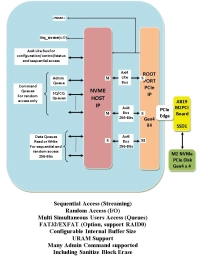

ARTIX Ultra Scale Plus NVME HOST IP – Gen4

- When using a PCIe RP IP configured in Gen4 the system frequency is at 250MHz/256-Bits.

- When using a PCIe RP IP configured in Gen3 the system frequency is at 125MHz/256-Bits.

-

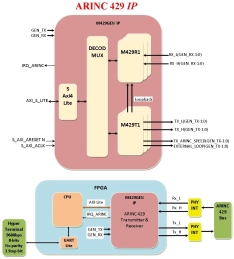

ARINC 429 IP

- The M429GEN IP implements a synchronous single-chip ARINC 429 Transmit and Receive Controller capable of linking one CPU to one or several ARINC 429 bus.

- The IP controls all ARINC 429 bus specific sequences, protocol and timing. The M429GEN IP interface allows the parallel-bus microprocessor to communicate bidirectionally with the ARINC 429 bus.

-

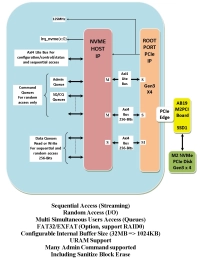

Kintex Ultra Scale Plus NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using AXI bus.

-

AGILEX 7 R-Tile Gen5 NVMe Host IP

- The LDS NVME HOST IP has been done for beginners and expert in NVMe to drive NVMe PCIe SSD.

- The register file interface simplify the management of the IP for CPU interface or State Machine interface using Avalon bus.

-

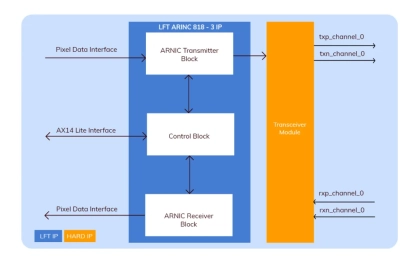

ARINC 818-3 IP Core

- Compliant to ARINC818-3 Specification. The max speed supported is 28 Gbps.

- Built on Fiber Channel Audio Video protocol.

- Point-to-Point Video/Data Transmission support using 64B/66B and 256B/257B Encoding over the serial link.

- Supports both optical and electrical links.

-

32x1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V Logic Process

- Fully compatible with MXIC 0.18um 1.8V/5V logic process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD

-

32x1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V Logic Process

- Fully compatible with MXIC 0.18um 1.8V/5V logic process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD

-

64x8 Bits OTP (One-Time Programmable) IP, Nexchip 0.15um 3.3V Logic Processes

- Fully compatible with Nexchip 0. 15um 3.3V logic processes

- Wide operating voltage range:

- – Read voltage: 1.62–3.63 V VDD and VDDP

- – Program Voltage: 3.45 V ± 5% VDDP and 1.62–3.63 V VDD

-

32x1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V Logic 18A Process

- Fully compatible with MXIC 0.18um 1.8V/5V logic 18A process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD