Multimedia IP

Filter

Compare

203

IP

from

39

vendors

(1

-

10)

-

China Multimedia Mobile Broadcasting (CMMB) LDPC decoder

- Compliant with China Multimedia Mobile Broadcasting (CMMB) specifications

- Near floating point error correction performance

- Early iteration stopping feature

- Patented architecture allowing high throughput for reduced footprint

-

Hyper-Bandwidth Multichannel Memory Subsystem

- Hyper-Bandwidth Multi-Channel - The fastest, most observable LPDDR3 subsystem you can drop into an SoC

- Supports an aggressive bandwidth envelope for LPDDR3, JEDEC-2133Mbps and up to 3200 Mbps on select process nodes.

- Includes hard QoS enforcement, traffic shaping, performance observability & self-tuning PHY front-end.

-

SD Card Input/Output Protocol Controller

- Compliance with Embedded MultiMediaCard System Specification Version 4.51. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (backward compatibility)

- Full compliance with SD memory card specifications version 4.2 ( SPI mode and UHS-II mode not supported)

-

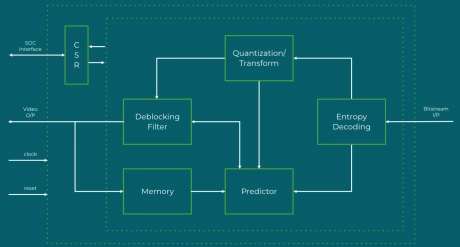

H.265 Decoder

- The H.265 (HEVC – High Efficiency Video Coding) Decoder IP core delivers high-performance video decompression for next-generation visual applications, including broadcast, surveillance, automotive, and consumer electronics.

- It supports real-time decoding of ultra-high-definition (UHD) video streams, up to 4K and 8K resolutions, while significantly reducing bandwidth and storage requirements without compromising video quality.

-

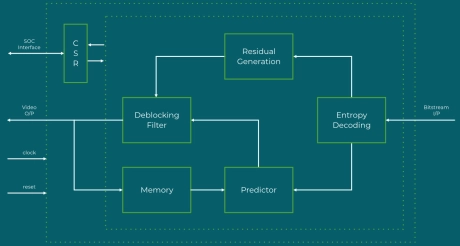

H.264 Decoder

- Thes H.264 Decoder IP Core offers a high-efficiency video decoding solution tailored for a wide range of applications, including multimedia, surveillance, broadcast, and automotive systems.

- Compliant with the ITU-T H.264/AVC standard, it enables real-time decoding of high-definition video streams while maintaining low latency and power consumption.

-

DP 1.4 Transmitter PHY

- The DisplayPort 1.4 Transmitter PHY is for transmitting high-definition video and audio, making it an ideal choice for a wide range of applications from gaming and professional graphics to digital signage and broadcasting.

- Its high bandwidth, support for ultra-high resolutions, and robust feature set make it a critical component for any high-performance multimedia system.

-

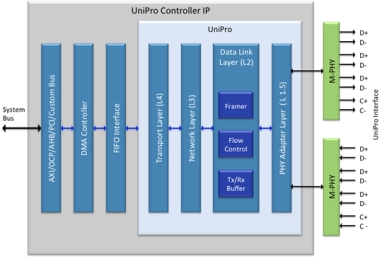

UniPro℠ Controller IP Core

- The UniPro Controller IP core is fully compliant with the UniPro specification version 1.6 and supports the physical adapter layer of the M-PHY® specification.

- MIPI UniPro is a high-performance, chip-to-chip, serial interconnect bus for mobile applications. Designed to support up to 5Gbps per data lane, it is scalable from one to four bidirectional lanes.

-

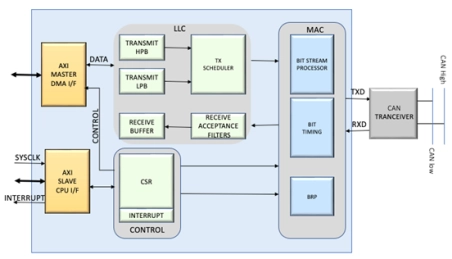

CAN FD Bus Controller IP

- The Controller Area Network – Flexible Data (CAN-FD) Controller IP implements the CAN 2.0A, CAN 2.0B as well as the high-performance CAN-FD (Flexible Data Rate) protocols.

- It is compliant to both Non-ISO CAN-FD from BOSCH as well as ISO11898-1:2015 DIS. It can be integrated into devices that require CAN connectivity commonly used in automotive and industrial applications.

-

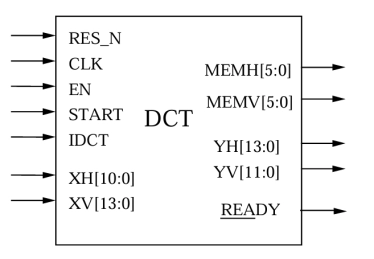

Discrete Cosine Transform

- This core can perform the two dimensional Discrete Cosine Transform (DCT) and its inverse (IDCT) on an 8x8 block of samples.

- The simple, fully synchronous design allows for fast operation while maintaining a low gate count.

- It offers high performance and many features to meet your multimedia, digital video and digital printing applications

-

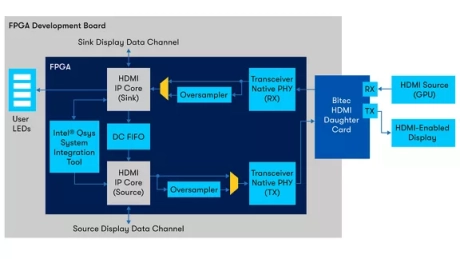

HDMI Intel® FPGA IP Core

- The HDMI Intel FPGA intellectual property (IP) core provides support for the next generation of video display interface technology

- Due to its ability to send high-definition audio and video, High-Definition Multimedia Interface (HDMI) has become the most common digital connection in consumer electronics.