Multi-port SDRAM Memory Controller IP

Filter

Compare

11

IP

from

7

vendors

(1

-

10)

-

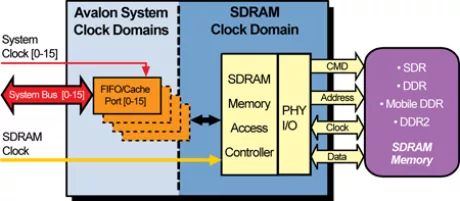

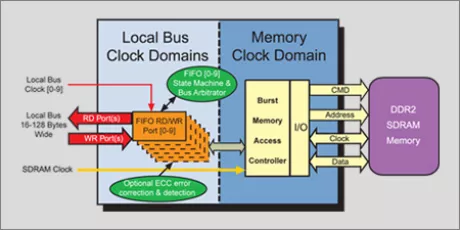

Streaming Multi-port SDRAM Memory Controller

- 200/333 MHz (400/666 Mbps) Cyclone / Stratix memory performance

- SDR, DDR, DDR2, and Mobile DDR SDRAM memory devices

- Up to 10 native RD or WR ports

- Memory data width: 8/16/32/64-bit

-

Avalon Multi-port SDRAM Memory Controller IP Core

- 200 / 333 MHz (400/666 Mbps) Cyclone / Stratix DDR2 memory performance

- SDR, DDR, DDR2 and Mobile DDR SDRAM Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

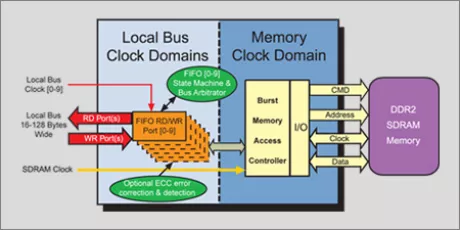

Multi-Port Memory Controller (DDR/DDR2/SDRAM)

- Soft Direct Memory Access (SDMA) support

- Double Data Rate (DDR/DDR2) and Single Data

- Rate (SDR) SDRAM memory support

- DIMM support (registered and unbuffered)

-

-

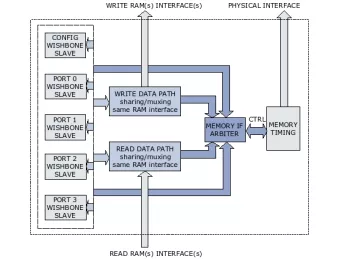

Avalon Multi-port DDR2 Memory Controller

- 200 / 333 MHz (400/666 Mbps) Cyclone/Stratix DDR2 memory performance

- DDR2 Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

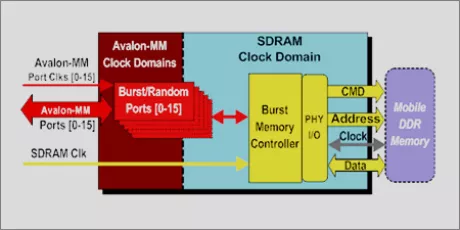

Avalon Mobile DDR Memory Controller

- 200 MHz Cyclone / Stratix memory performance

- Supports all standard Mobile DDR SDRAM devices

- 1 to 16 Avalon® independent local bus port interfaces

- Avalon Pipelined and Burst transfers

-

SDRAM DDR Controller

- Dolphin Technology offers high performance DDR4/3/2 SDRAM and LPDDR5/4x/4/3/2 SDRAM Memory Controller IP across a broad range of process technologies.

-

DDR3 SDRAM Controller IP with advance feautures package

- Supports DDR3 protocol standard JESD79-3F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR3 commands as per the specs. Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

LPDDR6/5X/5 Controller IP

- Supports JEDEC standard LPDDR6, LPDDR5X and LPDDR5 SDRAMs

- Support for data rates up to 14.4 Gbps for LPDDR6, 10.67 Gbps for LPDDR5X, and 6.4 Gbps for LPDDR5

- Multiport Arm® AMBA® interface AXI™4 with managed QoS or single-port host interface to the DDR controller

- DFI 5.2 compliant interface to Synopsys LPDDR6/5X/5 PHY

-

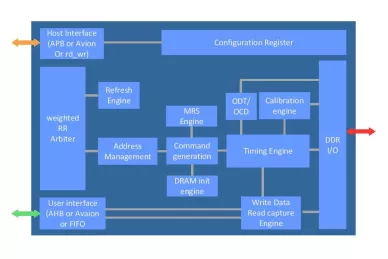

DDR-I/II/III CONTROLLER IP CORE

- Compliant with JEDEC Standard.

- Support up to 4 Gb and 8 banks of DDR2 devices.

- Application bus – FIFO, AHB, Avalon. Support multiple agents on application bus interface with built-in credit/aging based weighted round robin arbitration scheme.

- Programmable CAS latency and DRAM timing parameters.