Multi-Card Controller IP

Filter

Compare

73

IP

from

30

vendors

(1

-

10)

-

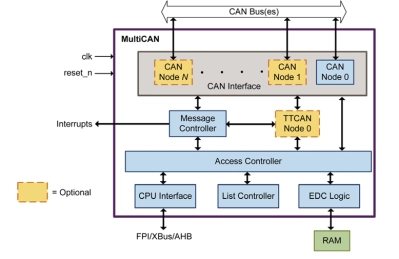

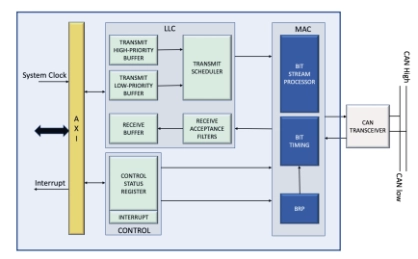

MultiCAN Controller

- MultiCAN improves upon previous CAN implementations, including TwinCAN, by adding features such as additional CAN nodes, more message objects, linked list management of message objects, and support for TTCAN level 2.

- For backward compatiblity, you can configure MultiCAN to provide features and functionality similar to TwinCAN.

- MultiCAN is available in technology-independent, fully synthesizable source code with your choice of host processor bus interfaces: Infineon FPI, XBus, or AMBA APB.

-

Gigabit Ethernet Controller

- XEC is a high performance 1000M/100M/10M Ethernet Controller IP. It support GMII/RGMII/MII/RMII MAC-PHY interface and support AXI/AHB system bus.

- XEC can receive the data from Ethernet PHY to the AXI/AHB bus, and to send out data from AXI/AHB bus to the Ethernet PHY.

-

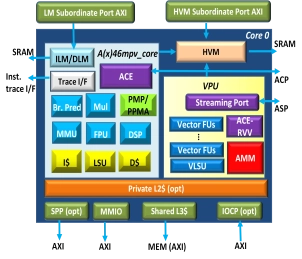

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

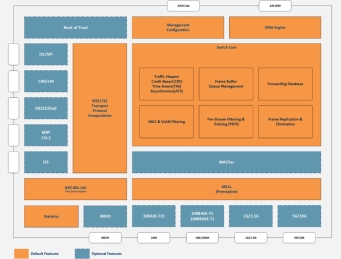

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

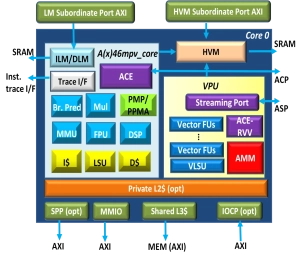

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

CAN-XL Bus Controller IP

- The CAN-XL Bus Controller Core performs serial communication as per CAN 2.0, CAN-FD & CAN-XL Specifications.

- It also supports original Bosch Protocol & ISO 11898 specifications for TTCAN (Time Triggered Operation) as specified in ISO11898-4.

- The design is fully optimized to support AUTOSAR and SAE J1939 specifications.

-

Host controller IP for controlling flash and other devices on the SPI bus: Quad SPI, Octal SPI, and xSPI

- Flexibility: Multiple SPI protocol support within single IP

- Simplicity: PHY-less IoT operation, or soft storage combo PHY IP simplifies SoC timing

- High Performance: Supports maximum Quad SPI / Octal SPI data rates and XIP (Execute In Place)

-

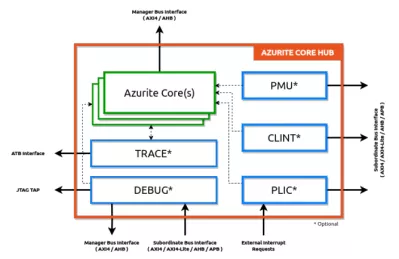

32b/64b RISC-V 2-stage, scalar, in-order, Embedded Processor. RTOS and multi-core capable. Maps upto ARM M-4F. Optimal PPA.

- 32-bit RISC-V core

- 2-stage pipeline

- Available in many versions: RV32I[M][C][F][B][P][U]

- 32/16 general purpose registers

-

Superscalar Out-of-Order Execution Multicore Cluster

- 64-bit out-of-order 4 wide decode 13-stage CPU core with 128 reordering buffers and 8 functional pipelines

- Symmetric multiprocessing up to 8 cores

- Level-2 cache and coherence support

- AndeStar™ V5 Instruction Set Architecture (ISA)

- 64-bit architecture for memory space over 4GB

- TAGE Branch predication for highly accurate prediction

-

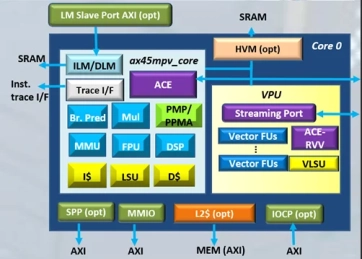

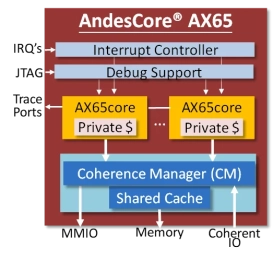

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores