Media Local Bus Interface IP

Filter

Compare

14

IP

from

7

vendors

(1

-

10)

-

Media Local Bus Interface

- Adds MOST® connectivity to Xilinx® FPGAs

- Licensed MediaLB® technology from SMSC®

- Compliant with the MLB Specification Version 4.2

- Supports 3-pin and 6-pin interface to INICs

-

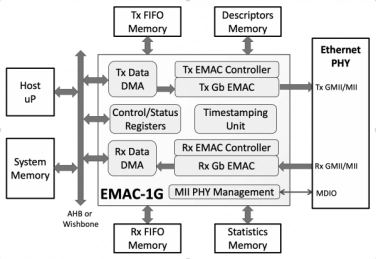

Gigabit Ethernet Media Access Controller

- Implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- The controller provides half- or full-duplex operation, supports jumbo frames, and optionally provides a useful set of statistics counters enabling station management.

- Furthermore, the core can optionally be configured with a hardware timestamping unit enabling support for the IEEE 1588 precision time protocol (PTP).

-

XPS Ethernet Lite

- PLB interface is based on PLB v4.6 specification

- Memory mapped direct I/O interface to the transmit and receive data dual port memory

- Media Independent Interface (MII) for connection to external 10/100 Mbps PHY transceivers

- Independent internal 2K byte Tx and Rx dual port memory for holding data for one packet

-

XPS_LL_TEMAC

- Independent 2K, 4K, 8K, 16K, or 32K Byte TX and RX data FIFOs for queueing frames

- Filtering of "bad" receive frames

- Support for several PHY interfaces

- Media Independent Interface Management access to PHY registers

-

Ethernet MAC Controller IP

- Compliant to IEEE 802.3-2002 specification

- Comply with IEEE 802.3u MII interface.

- Supports full duplex flow control - IEEE 802.3

- Supports VLAN - compliant to IEEE 802.3, 802.1Q

-

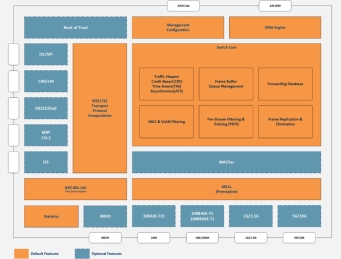

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

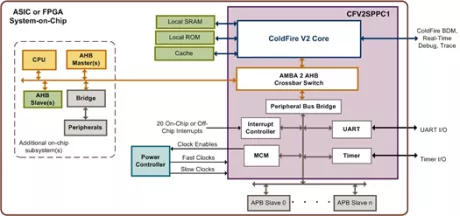

ColdFire V2 Core with AMBA peripherals connected in a subsytem

- Building upon the 68K foundation, ColdFire offers RISC performance with industry-leading code density and a rich set of connectivity peripherals.

- By supporting variable-length instructions (16-, 32- or 48-bits long), the ColdFire Architecture enables higher code density than traditional 32- and 64-bit RISC machines.

- More efficient use of on-chip memory reduces bus bandwidth and external memory requirements, resulting in lower system cost.

-

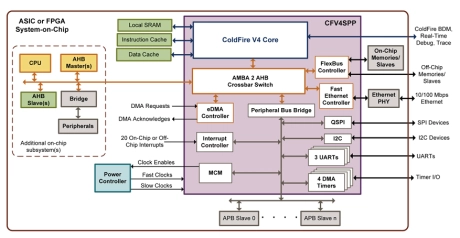

ColdFire V4 Core & Standard Product Platform

- The ColdFire V4 Core & Standard Product Platform (CFV4SPP) combines the ColdFire V4 Core with industry-proven platform peripherals to form a complete high-performance micro-controller subsystem supported by a vast ecosystem of development tools and runtime software.

-

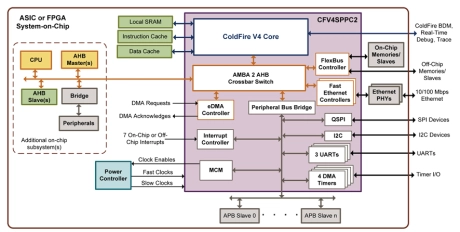

ColdFire V4 Core & Standard Product Platform (SPP) C2

- The ColdFire V4 Core & Standard Product Platform (SPP) C2 (CFV4SPPC2) combines the ColdFire V4 Core with industry proven platform peripherals to form a complete high performance micro-controller subsystem supported by a vast ecosystem of development tools and runtime software.

-

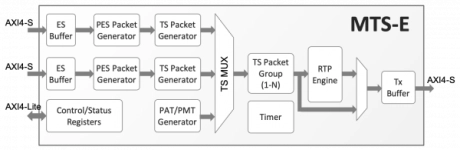

MPEG Transport Stream Multiplexing & Encapsulation Engine

- The MTS-E core multiplexes and encapsulates audio, video, and metadata streams in a single MPEG Transport Stream (MTS), and optionally encapsulates the TS packets in Real-Time Transport Protocol (RTP) packets.

- Under its default configuration, the MTS-E multiplexing and encapsulation engine supports two input stream channels, e.g., one Audio and one Video.