MIPI DSI-2 Controller IP

Filter

Compare

25

IP

from

7

vendors

(1

-

10)

-

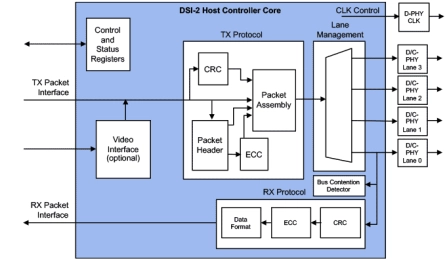

MIPI DSI-2 Controller Core

- Fully MIPI DSI-2/DSI standard compliant

- 64 and 32-bit core widths

- Host (Tx) and Peripheral (Rx) versions

- Supports 1-4, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

-

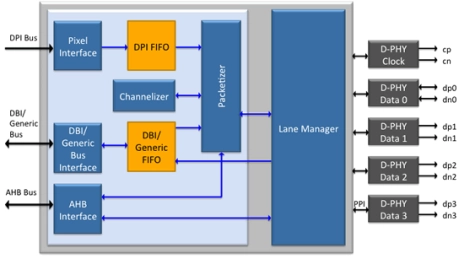

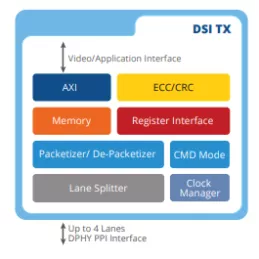

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

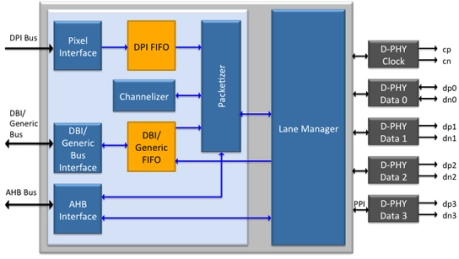

MIPI DSI-2 Receiver IP Controller Core

- The MIPI Display Serial Interface (DSI-2) Receiver (display panel interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

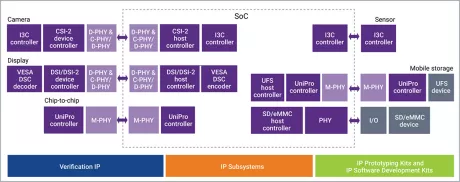

MIPI DSI-2 V2 Host Controller Prem

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 V2 Host Controller ASIL Compliant

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 Transmitter v1.1 Controller IP, Compatible with MIPI D-PHY & C-PHY

- Compliant with MIPI DSI-2 Standard v0.8.x, MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C-PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration

-

MIPI DSI-2 High Performance Device Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 High Performance Device Combo Controller for Automotive

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 High Performance Device Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

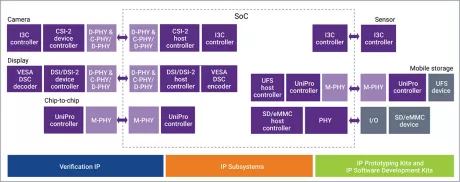

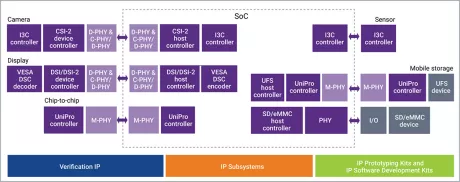

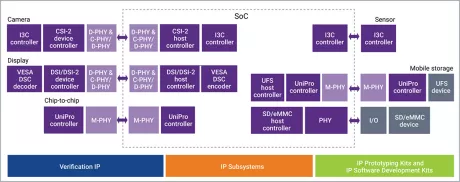

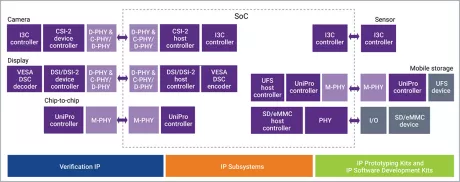

MIPI DSI-2 controllers with VESA DSC for high-speed serial interface between application processor and displays