MIPI DSI-2 IP

Filter

Compare

55

IP

from

15

vendors

(1

-

10)

-

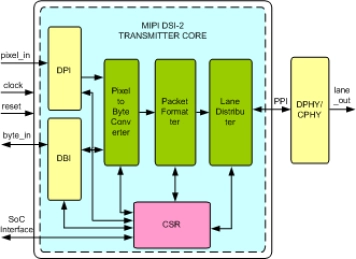

MIPI DSI-2 Transmitter Controller IP Core

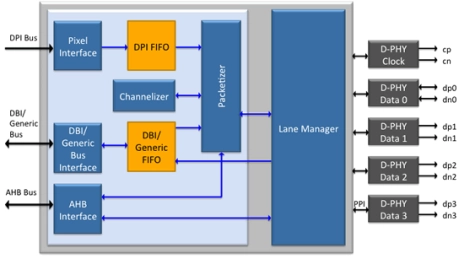

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

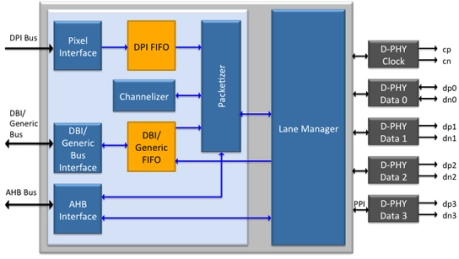

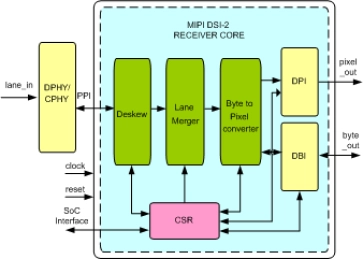

MIPI DSI-2 Receiver IP Controller Core

- The MIPI Display Serial Interface (DSI-2) Receiver (display panel interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

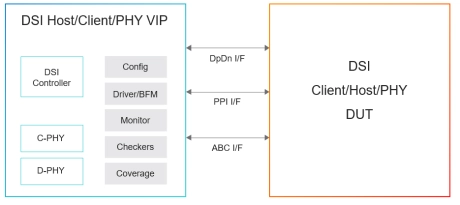

Simulation VIP for MIPI DSI-2

- Receiver and Transmitter Verification

- Verifies both DSI processor and peripheral

- Physical Layer

- Includes the MIPI D-PHYsm/C-PHYsm VIP for physical layer verification

-

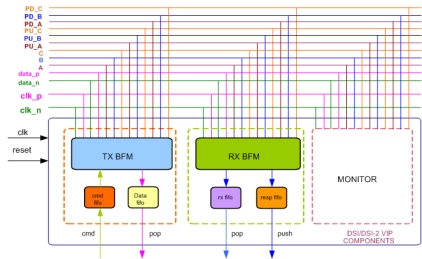

MIPI DSI-2 Verification IP

- Full MIPI DSI-2 Tx and Rx functionality.

- Supports 2.0 MIPI DSI-2 Specification.

- Support both DPHY and CPHY

- Supports MIPI DBI specification

-

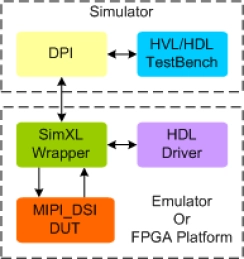

MIPI DSI-2 Synthesizable Transactor

- Full MIPI DSI-2 Tx and Rx functionality.

- Supports MIPI DSI-2 Specification.

- Support both DPHY and CPHY

- Supports MIPI DBI specification

-

MIPI DSI-2 Transmitter IIP

- Compliant with MIPI DSI-2 Specification v1.3

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2

- Compliant with Display Pixel Interface (DPI -2) v 2.0

-

MIPI DSI-2 Receiver IIP

- Compliant with MIPI DSI-2 specification v1.3

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2

- Compliant with Display Pixel Interface (DPI -2) v 2.0

-

MIPI DSI-2 V2 Host Controller Prem

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 V2 Host Controller ASIL Compliant

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 High Performance Device Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1