MIPI CSI-2 v3.0 IP

Filter

Compare

9

IP

from

6

vendors

(1

-

9)

-

MIPI CSI-2 v3.0 Rx/Tx For Combo C/D-PHY

- Compliant with MIPI CSI Standard v3.x, v2.x , v1.x and MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C-PHY V1.x

-

MIPI CSI-2 v3.0 TRANSMITTER FOR COMBO C/DPHY

- Compliant with MIPI CSI Standard v3.x, v2.x, v1.x and MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C- PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios.

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration.

-

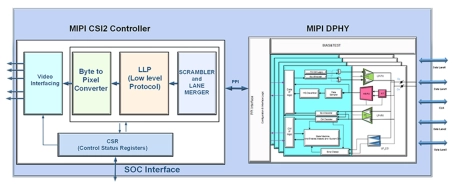

MIPI CSI2 Interface Solution

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

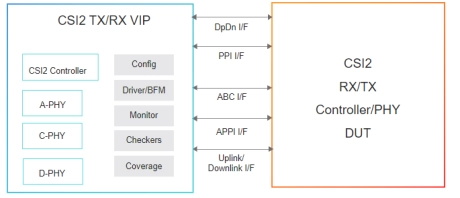

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

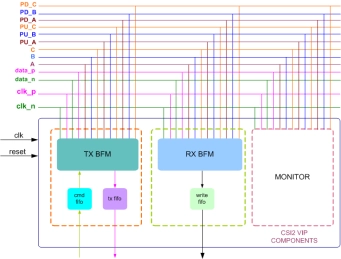

MIPI CSI-2 Verification IP

- Full MIPI CSI2 Tx/Rx functionality

- Compliant with MIPI CSI2 Bus Specification v1.0 to v1.3, v2.0 to v2.10,v3.0,v4.0.

- Supports both DPHY and CPHY.

- Supports forward escape ULPM on all Data Lanes.

-

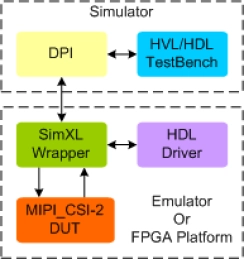

MIPI CSI-2 Synthesizable Transactor

- Supports 3.0 MIPI CSI-2 Specification.

- Compliant with MIPI CSI2 Bus Specification v1.0 to v1.3, v2.0 to v2.10, v3.0.

- Full MIPI CSI2 Tx/Rx functionality

- Support both DPHY and CPHY.

-

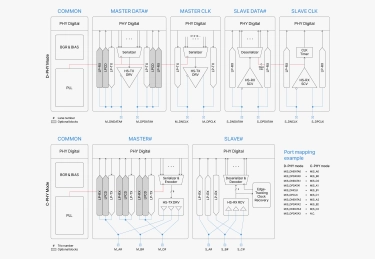

MIPI C/D-PHY Combo IP

- Compliant to MIPI D-PHY v3.0, C-PHY v2.1 specification

- Area efficient macro optimized for placement for dense SoC designs

- Support Uni-(TX or RX) and Bi-directional(TX and RX) mode

- Support emphasis architecture over lossy channel for TX

- Support equalize architecture over lossy channel for RX

-

GLOBALFOUNDRIES 22nm FDX MIPI CDPHY Master V2.1/V3.0

- GLOBALFOUNDARIES 22nm FDSOI 0.8V/1.8V

- 80 to 6000 Mbps data rate per lane in DPHY HS mode

- 0 to 4500 Msps symbol rate per lane in CPHY HS mode

-

GLOBALFOUNDRIES 22nm FDX MIPI CDPHY Master V2.1/V3.0

- Process: GLOBALFOUNDARIES 22nm FDSOI 0.8V/1.8V

- 80 to 6000 Mbps data rate per lane in DPHY HS mode

- 80 to 4500 Msps symbol rate per lane in CPHY HS mode

- All lanes support HS and ULPS modes in forward direction