LEON3 IP

Filter

Compare

3

IP

from

1

vendors

(1

-

3)

-

32-bit SPARC V8 processor

- The LEON3 processor offers robust fault tolerance and performance for space and high-reliability applications, including satellites and scientific instruments.

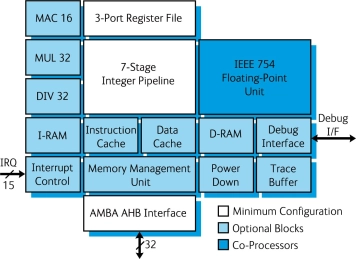

- The LEON3 is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The model is highly configurable and particularly suitable for system-on-a-chip (SOC) designs.

-

32-Bit SPARC V8 Processor

- SPARC V8 instruction set with V8e extensions and compare-and-swap

- Advanced 7-stage dual-issue pipeline

-

Configurable AMBA bus SoC platform

- Robust and fully synchronous single-edge clock designs

- Up to 125 MHz in FPGA and 400 MHz on 0.13 um ASIC technologies

- Fault-tolerant and SEU-proof version

- Symmetric Multi-processor support (SMP)