LCD Controller IP

Filter

Compare

47

IP

from

15

vendors

(1

-

10)

-

Display Controller – LCD / OLED Panels (Avalon Bus)

- The DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the Avalon Bus within Altera Qsys Integration (generating the System Interconnect Fabric) to a TFT LCD panel.

- In an Altera FPGA, typically, the microprocessor is a NIOS II or ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

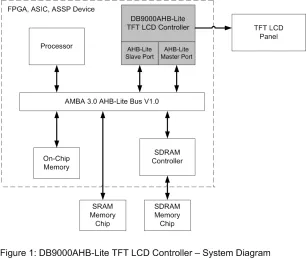

Display Controller - LCD / OLED Panels (AHB-Lite Bus)

- The Digital Blocks DB9000AHB-Lite TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the AMBA 3.0 AHB-Lite Bus V1.0 to a TFT LCD panel.

- In an FPGA, ASIC, or ASSP device, the microprocessor is typically an ARC, ARM, Intel, MIPS, OpenSPARC, PowerPC, or Tensilica processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

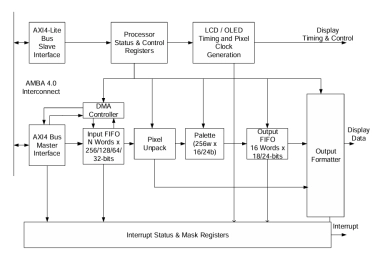

Display Controller - LCD / OLED Panels (AXI4 Bus)

- Advanced display processing, such as Multi-layer Overlay Windows with composition features such as Alpha Blending, Color Space Conversion, 4:2:0 and 4:2:2 YCrCb color with Re sampling & conversion to RGB, Frame Buffer Compression and Hardware Cursor

-

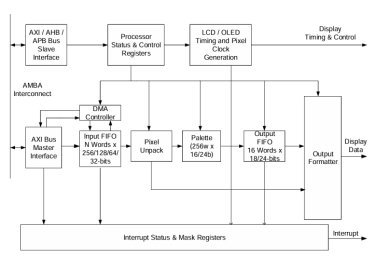

Display Controller - LCD / OLED Panels (AXI Bus)

- The Display Controller Verilog RTL IP Core comes in releases supporting baseline display processing features and releases with advanced display processing, such as Multi layer Overlay Windows with optional Alpha Blending, Scaling, Color Space Conversion, 4:2:0 and 4:2:2 YCrCb with Re-sampling & conversion to RGB, and Hardware Cursor and Frame Buffer Compression. Optional features provide the customer with targeted features while saving on VLSI resources and licensing costs.

- The DB9000AXI3 contains a selectable 256 / 128 / 64 / 32-bit AXI Master Interface with the higher data widths targeting higher resolution, higher color depth LCD or OLED display panels, with their resulting high frame buffer memory data bandwidth requirements.

-

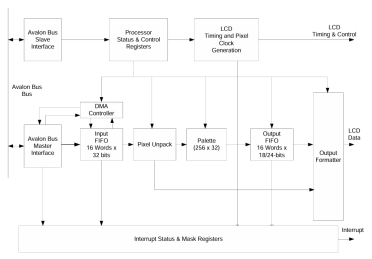

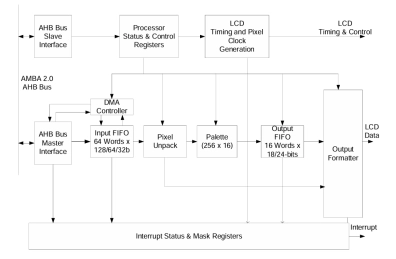

AHB TFT LCD Controller w/ DMA

- The AHB TFT LCD Controller is a configurable core that interfaces to an AHB microprocessor bus and provides all the timing control and pixel serialization for controlling various TFT LCD Display Panels.

- The core can also be used with various RAMDACs to interface to VGA Monitors or VGA style LCD Panels.

- The AHB TFT LCD Controller supports 24-bit true color and 16-bit color, as well as an 8-bit color display mode via the 256 Pixel Palette Ram.

-

Display Controller - LCD / OLED Panels (AHB Bus)

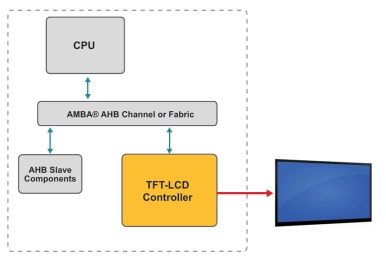

- The DB9000AHB TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the AMBA 2.0 AHB Bus to a TFT LCD panel.

- In an FPGA, ASIC, or ASSP device, the microprocessor is an ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

LCD Display controller

- 24-bit RGB or 20-bit BT1120 parallel pixel output; 8 bits-per-pixel (RGB888)

- 1 display FIFO (32x24-bit)

- Color look-up table (CLUT) up to 256 color (256x24-bit) per layer

- Programmable timings for different display panels (Refer to :ref:Synchronou_timing)

-

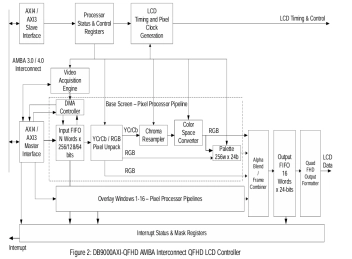

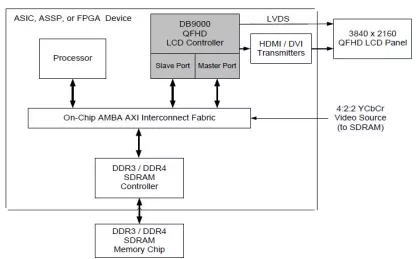

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

Display Controller – 4K Digital Cinema LCD Panels (AXI4/AXI Bus)

- The DB9000AXI-DCI LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to a 4K and 2K Digital Cinema Initiative (DCI) High Definition TFT LCD panel

- The video image in frame buffer memory can be 8/10/12-bit YCrCb or RGB, with a Color Space Convert to match the source video to the TFT LCD panel requirements

-

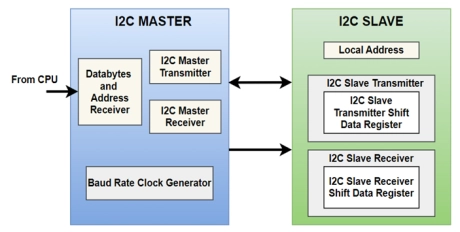

I2C - Function Controller

- The I2C (Inter - Integrated Circuit) protocol is a widely used serial communication protocol for transferring data between electronic devices. It was developed by Philips in the 1980s and is now owned by NXP Semiconductors. I2C uses two bidirectional data lines called SDA (Serial Data) and SCL (Serial Clock) for communication between devices.

- It allows multiple devices to be connected to the same bus, and each device can be identified by a unique address. The protocol supports data transfer rates ranging from a few kilobits per second to several hundred kilobits per second.