JESD204D IP

Filter

Compare

7

IP

from

3

vendors

(1

-

7)

-

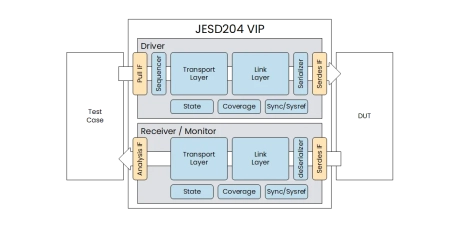

JESD204D Verification IP

- Truechip JESD204D VIP is compliant to the latest JESD204D,C.01,C &B specification by JEDEC

- It is also backward compatible with all the previous versions of JESD204

- Supports a wide range configurations for data converter devices

- Over single and multiple serial links with each link can support single or multiple lanes as per requirements

-

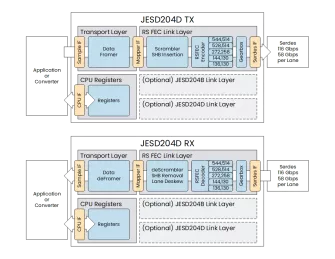

JESD204D Controller IP

- Line rates up to 116 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

- HD-mode supported

-

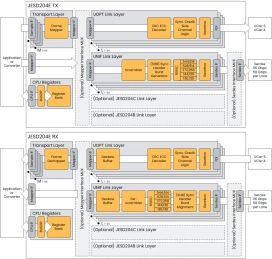

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.

-

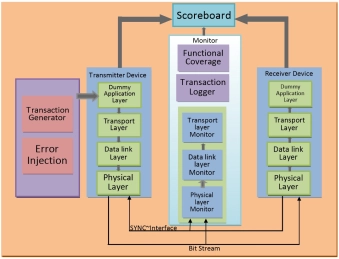

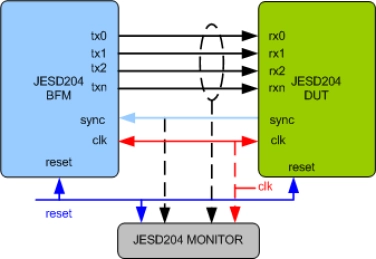

JESD204 Verification IP

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.

-

JESD204 Verification IP

- Follows JESD204 specification JESD204A, JESD204B, JESD204C and JESD204D.

- Supports Transmitter and Receiver Mode.

- Supports data interfaces up to 116 Gbps with PAM4 and up to 58 Gbps with PAM2 in PHY layer.

- Supports up to 32 lanes.

-

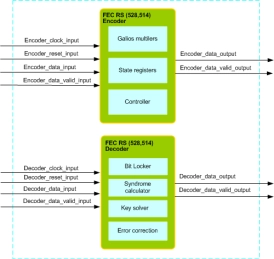

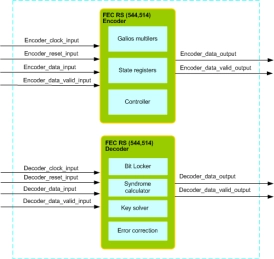

FEC RS (544,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (544,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.

-

FEC RS (528,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (528,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.