HDR ISP IP

Filter

Compare

14

IP

from

7

vendors

(1

-

10)

-

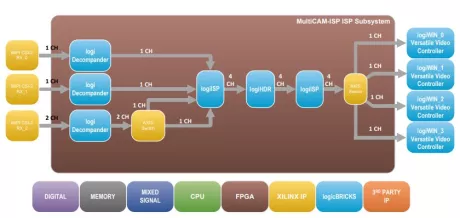

HDR ISP framework for multi-camera applications

- Complete HDR ISP video processing framework for multi-channel vision and AI systems

-

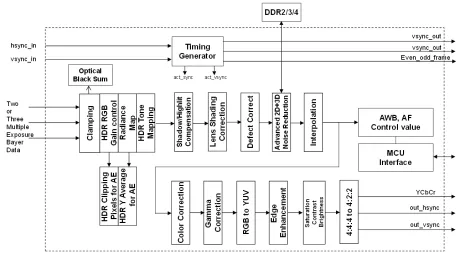

Multiple Pixel Processing Camera Image Signal Processing Core

- Support RGB Bayer progressive image sensor and Monochrome progressive image sensor

- Support 8 ~ 14 bit input data Bayer

-

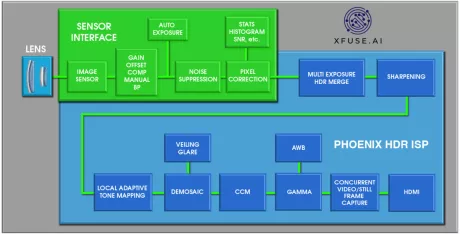

HDR Image Signal Processor

- Advanced motion compensation algorithms virtually eliminate HDR merge artifacts and transition noise

- Proprietary Locally Adaptive Tone Mapping technology

-

Low-Power ISP

- The Image Signal Processing (ISP)-- ISI700 receives camera sensor data via the 4-channel DVP interface

- It is designed for multi-camera, multi-exposure high dynamic range (HDR) image signal processor (ISP) for the mid- to high-end consumer and surveillance market

- The ISI700 offers the following functions: It brings advanced imaging technologies and chromatic aberration correction to provide unrivalled image quality and support to a large number of HDR sensor formats

-

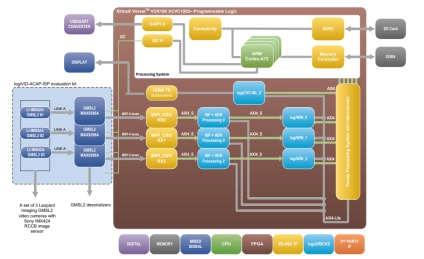

ACAP HDR Image Signal Processing Framework

- The ACAP HDR Image Signal Processing Framework is intended to showcase a complete logicBRICKS IP suite implementation of High-Dynamic Range (HDR) Image Signal Processing (ISP) pipeline in an embedded design based on AMD-Xilinx ACAP programmable devices.

- The HDR ISP pipeline enables crisp camera video under altering and rough lighting conditions in next generation multi-channel embedded systems for use in automotive, surveillance, medical, aerospace and similar video and vision AI applications.

-

High Dynamic Range (HDR) Pipeline

- Digitally processes and enhances raw image data from HDR camera sensors

- Supports Xilinx® Zynq®-7000 AP SoC, 7 Series and newer

-

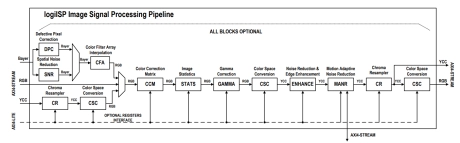

UHD Image Signal Processing (ISP) Pipeline

- The logiISP-UHD Image Signal Processing Pipeline IP core is an Ultra High Definition (UHD) ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx ACAP, MPSoC, SoC and FPGA devices.

- It enables parallel processing of multiple Ultra HD video inputs in different programmable devices, ranging from the small Xilinx Artix®-7 FPGAs to the latest Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) devices.

-

Image Signal Processor IP

- Support 8-16 Bit Bayer RAW and ITU-R BT.601 & 656 Video Interface

- Test Pattern Generator(TPG)

- Black Level Measurement and Compensation (BLS)

- Sensor linear correction

-

Image Signal Processor IP - High performance image signal processing for auto and industrial markets

- 32bit DVP interface, 24bit ISP pipeline

- Dual pixel per cycle throughput

- Wide Dynamic Range Tone Mapping (WDR)

- Multi-exposure HDR (Native/build in HDR, Compand output, DOL/Stagger, Stagger output)