HBM2 Controller IP

Filter

Compare

17

IP

from

6

vendors

(1

-

10)

-

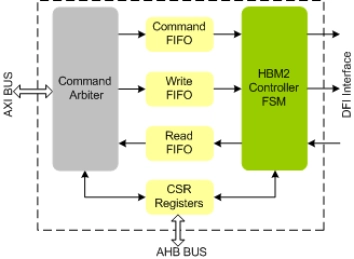

HBM2 Controller IIP

- Supports HBM2 protocol standard JESD235 and JESD235A Specification

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

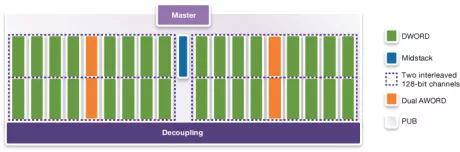

HBM2 Memory Controller

- Support Pseudo Channel mode with 64DQ per Pseudo Channel

- Support DFI1:1

- Support HBM Burst Length 4

- Support 4 High or 8 High HBM Devices

-

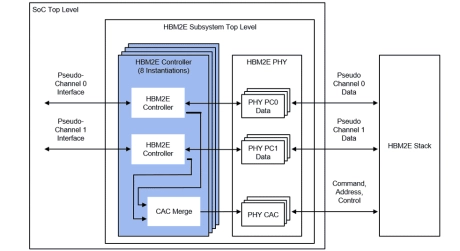

HBM2/2E Memory Controller Core

- Supports HBM2E and HBM2 devices

- Supports all standard HBM2/2E channel densities (4, 6, 8, 12, 16, 24 Gb)

- Supports data rates of up to 3.6 Gbps/pin

- Can handle two pseudo-channels with one controller or independently with two controllers

- Queue-based interface optimizes performance and throughput

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

-

HBM2E and HBM2 FPGA IP

- HBM2E and HBM2 are high-performance memory IPs that offer a combination of high memory bandwidth, low power consumption, low latency, and small form factor for Agilex™ 7 FPGA M-Series and Stratix® 10 MX FPGAs, respectively

- HBM2E and HBM2 are well-suited for a variety of high-performance computing applications.

-

DDR and LPDDR 5/4/3/2 controllers for low power and high Reliability, Availability and Serviceability (RAS)

- Four memory controller offerings: uMCTL2: multi-ported memory controller supporting JEDEC standard DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4, and LPDDR4X SDRAM and DIMM modules

- uPCTL2: Single-ported version of uMCTL2 with no internal scheduler; DDR5/4 controller: multi-ported memory controller supporting JEDEC standard DDR5, DDR4 SDRAMs and DIMM modules

- LPDDR5/4/4X controller: multi-ported memory controller supporting JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- High-bandwidth design with up to 64 CAM entries for Reads and 64 CAM entries for Writes, and latency as low as 6 clock cycles

-

DDR and LPDDR 5/4/3/2 controllers for low power and high Reliability, Availability and Serviceability (RAS) targeting automotive

- Four memory controller offerings: uMCTL2: multi-ported memory controller supporting JEDEC standard DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4, and LPDDR4X SDRAM and DIMM modules

- uPCTL2: Single-ported version of uMCTL2 with no internal scheduler; DDR5/4 controller: multi-ported memory controller supporting JEDEC standard DDR5, DDR4 SDRAMs and DIMM modules

- LPDDR5/4/4X controller: multi-ported memory controller supporting JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- High-bandwidth design with up to 64 CAM entries for Reads and 64 CAM entries for Writes, and latency as low as 6 clock cycles

-

TSMC CLN7FF HBM2E PHY IP

- High Bandwidth Memory (HBM2E) DRAM PHY

- Supports HBM 3.2Gbps

- Supports DFI 1:2

- Supports only BL4

-

TSMC CLN5FF HBM PHY IP

- High Bandwidth Memory (HBM) DRAM PHY

- Supports HBM 3.6Gbps

- Supports DFI 1:2

- Supports only BL4

-

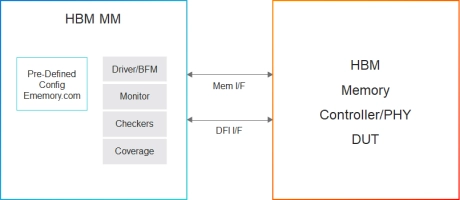

Simulation VIP for HBM

- Speed (MHz)

- 1800MHz (3.6 Gbps/pin)

- Device Density

- Supports a wide range of device densities from 1Gb to 24Gb

-

HBM2E PHY V2 - TSMC N5

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps