GDDR5 IP

Filter

Compare

11

IP

from

2

vendors

(1

-

10)

-

GDDR5 Controller - Verifies memory compliance, boosts performance, and ensures reliability

- The GDDR5 Memory Controller Verification IP (VIP) is a robust solution designed to verify the compliance and performance of GDDR5 memory controllers. It ensures adherence to GDDR5 specifications, enabling high-speed data transfers, low latency, and power efficiency for advanced systems.

- This VIP is vital for applications requiring high data throughput and low latency, such as GPUs, gaming consoles, VR systems, HPC, AI accelerators, and data centers. It ensures reliable, high-performance memory operations across a variety of demanding use cases

-

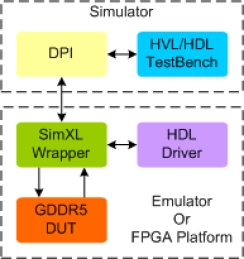

GDDR5 Synthesizable Transactor

- Supports 100% of GDDR5 protocol standard JESD212C

- Supports all the GDDR5 commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports up to 8GB device density

-

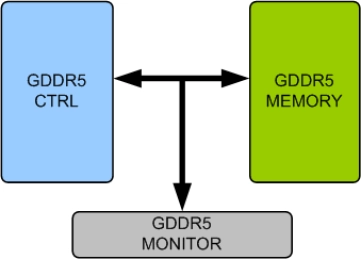

GDDR5 Memory Model

- Supports GDDR5 memory devices from all leading vendors.

- Supports 100% of GDDR5 protocol standard JESD212C.

- Supports all the GDDR5 commands as per the specs.

- Quickly validates the implementation of the GDDR5 standard JESD212 and JESD212C.

-

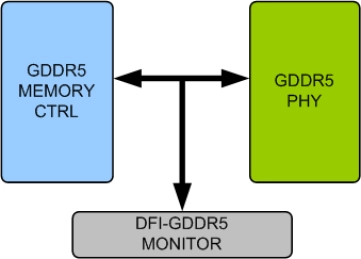

GDDR5 DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR5 devices compliant with JEDEC GDDR5 SGRAM Standard JESD212 and JESD212C.

- Supports all Interface Groups.

- Supports Write Transactions with Data mask.

-

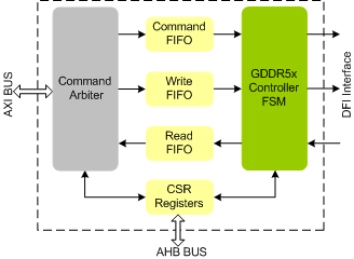

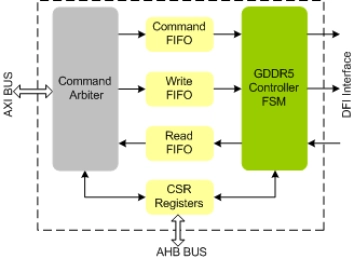

GDDR5 Controller IIP

- Supports GDDR5 protocol standard JESD212C.

- Compliant with DFI-version 4.0 or 5.0 Specification.

- Supports all the GDDR5 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

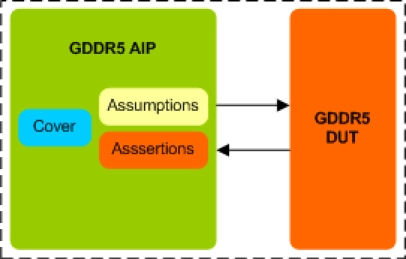

GDDR5 Assertion IP

- Specification Compliance

- Supports GDDR5 memory devices from all leading vendors.

- Supports 100% of GDDR5 protocol standard JESD212C.

- Supports all the GDDR5 commands as per the specs.

-

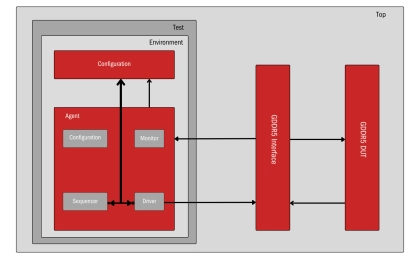

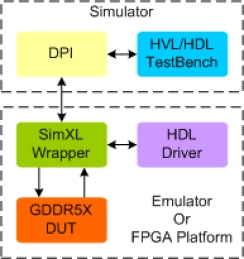

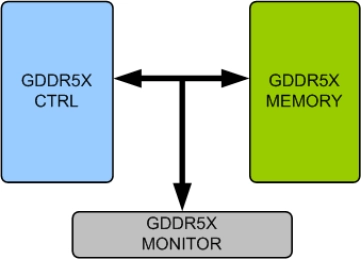

GDDR5X Synthesizable Transactor

- Supports 100% of GDDR5X protocol standard JESD232 and JESD232A

- Supports all the GDDR5X commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports up to 16GB device density

-

GDDR5X Memory Model

- Supports GDDR5X memory devices from all leading vendors.

- Supports 100% of GDDR5X protocol standard JESD232 and JESD232A.

- Supports all the GDDR5X commands as per the specs.

- Quickly validates the implementation of the GDDR5X standard JESD232 and JESD232A.

-

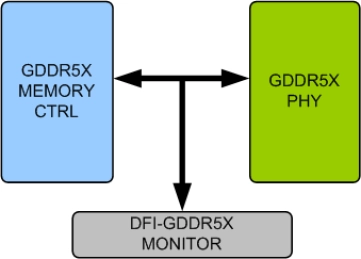

GDDR5X DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR5X devices compliant with JEDEC GDDR5X SGRAM Standard JESD232 and JESD232A.

- Supports all Interface Groups.

- Supports Write Transactions with Data mask.

-

GDDR5X Controller IIP

- Supports GDDR5X protocol standard JESD232 and JESD232A.

- Compliant with DFI-version 4.0 or 5.0 Specification.

- Supports all the GDDR5X commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.