Fibre Channel IP

Filter

Compare

17

IP

from

8

vendors

(1

-

10)

-

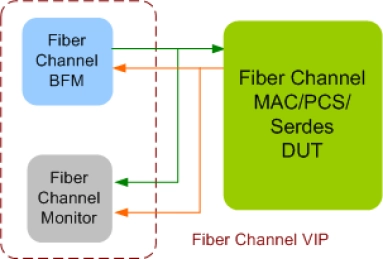

Fibre Channel Verification IP

- Compliant with the Fibre Channel framing and signaling specification FC-FS-6, Rev 0.1.

- Compliant with the Fibre Channel link service specification FC-LS-4, Rev 4.03.

- Compliant with the Fibre Channel physical interface specification FC-PI-7, Rev 0.13.

- Compliant with the Fibre Channel protocol for SCSI specification FCP-4.

-

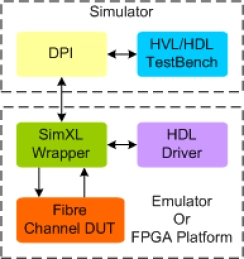

Fibre Channel Synthesizable Transactor

- Compliant with the Fibre Channel framing and signaling specification FC-FS-6, Rev 0.1.

- Compliant with the Fibre Channel link service specification FC-LS-4, Rev 4.03.

- Compliant with the Fibre Channel physical interface specification FC-PI-7, Rev 0.13.

- Compliant with the Fibre Channel protocol for SCSI specification FCP-4.

-

32G Fibre Channel (32GFC) Reed-Solomon Forward Error Correction

- Low latency design

- Configuration and status bus

- Example reference design demonstrating of RS-FEC and GT Wizard cores

- ECC RAM option

-

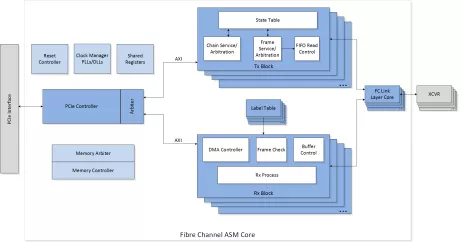

Fibre Channel ASM (Anonymous Subscriber Messaging) Core

- Message label validation checks performed in hardware

- Multiple user modes for receiving messages, including strictly mapped message-to-buffer and free-buffer implementations

- Transmit message chaining options provided

- Complete set of registers for managing core and configuring core options

-

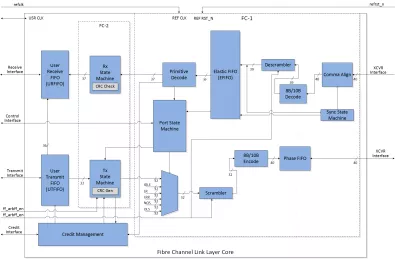

Fibre Channel Link Layer Core

- Complete FC1-FC2 functionality

- Intuitive streaming user interface

- Scales for multiple port designs

-

1.06/2.125/4.25 Gbps Fibre Channel and Backplane SerDes

- Quad SerDes optimized for Fibre Channel and backplane applications

- Supports data rates from 1.0625/2.125 and 4.25 Gbps speeds

- High-speed differential reference clock

- Low jitter clock synthesizers for clock distribution

-

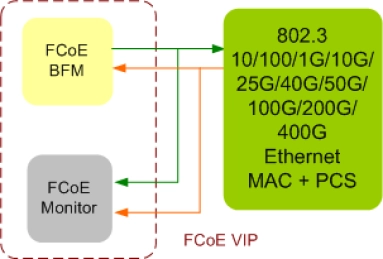

FCoE Verification IP

- Compliant with the latest Fibre Channel over Ethernet specification(FC-BB-5) Rev 2.00.

- Compliant with SCSI Architecture Model 3/4/5 (SAM-3/4/5).

- Supports N,F and E ports.

- Support for multiple initiators and targets.

-

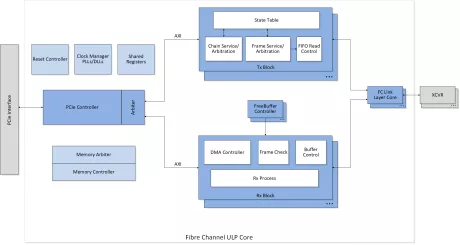

FC Upper Layer Protocol (ULP) IP Core

- FC-AE-RDMA & FC-AV compliant interface with hardware-based offload

- Hardware DMA engines map sequence data to host memory buffers

-

IEEE 802.3 Clause 74 FEC

- The IP core supports encoding and decoding of the (2112,2080) Fire code defined in IEEE 802.3 Clause 74

- Suitable for 10GBASE-R, 25GBASE-R, 40GBASE-R, 50GBASE-R and 100GBASE-R Ethernet PHYs and 16G Fibre Channel PHYs

- Burst errors of up to 11 bits can be corrected

- All alignment, transcoding, and scrambling functions are performed within the core

-

Virtex-6 FPGA GTX Transceiver Wizard

- Creates customized HDL wrappers to configure high-speed serial transceivers

- Predefined protocol templates support Aurora (8B/10B and 64B/66B), Common Packet Radio Interface (CPRI™), DisplayPort, Fibre Channel, Gigabit Ethernet, High-Definition Serial Digital Interface (HD-SDI), 3 Gb/s Serial Digital Interface (3G-SDI), Interlaken, Open Base Station Architecture Initiative (OBSAI), OC-48, PCI EXPRESS® (PCIe®) generation I and II, Serial Advanced Technology Attachment (SATA) 1.5 Gb/s, SATA 3 Gb/s, Serial RapidIO generation I and II, 10 Gb Attachment Unit Interface (XAUI), and RXAUI-Dune Networks

- Automatically configures analog settings