FEC IP

Filter

Compare

270

IP

from

52

vendors

(1

-

10)

-

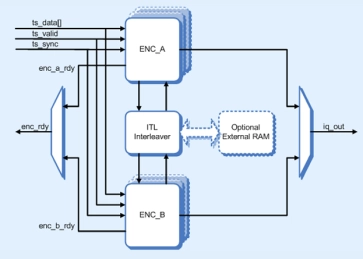

Multi-channel DVB-C / J83 FEC encoder

- The CMS0044 J.83abc/DVB-C Cable FEC Encoder combines all of the channel coding and Forward Error Correction functions specified by DVB-C and by J83 Annexes A B and C.

- It is designed to interface to external modulators or advanced upconverting DACs such as the Analog Devices AD9789.

-

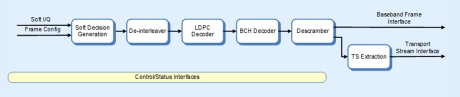

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

-

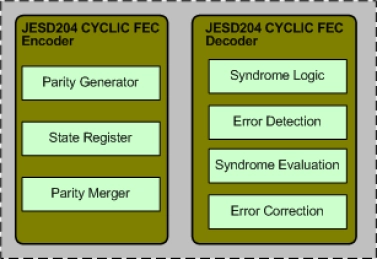

JESD204 CYCLIC FEC IIP

- Compliant with JESD204 specification JESD204C.

- Supports Full JESD204C FEC functionality.

- This FEC(Forward Error correction) methodology implements the (2074, 2048) binary cyclic code is shortened from the cyclic Fire code (8687, 8661).

- Supports FEC of 26 bits parity bits.

-

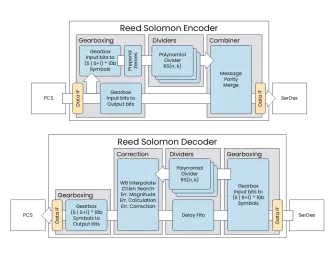

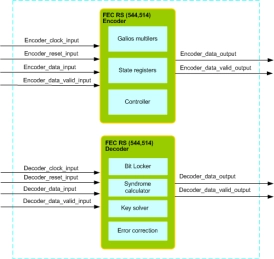

FEC RS (544,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (544,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.

-

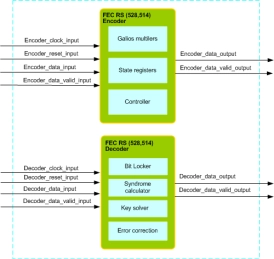

FEC RS (528,514) IIP

- Compliant with CPRI Specification V7.0, IEEE Standard 802.3.2018 Ethernet specification and JESD204D Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (528,514) FEC, 10-bit symbols.

- Supports different input and output data widths of multiples of 10-bits.

-

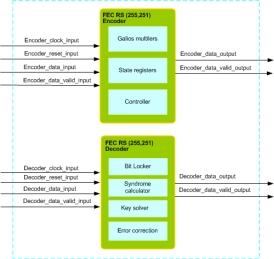

FEC RS (255,251) IIP

- HDMI specification 2.1/2.1a and Scalabale Low Voltage Signaling with Embedded Clock (SLVS_EC) compliant.

- Supports full FEC functionality.

- Supports Reed Solomon (255,251) FEC, 8-bit symbols.

- Supports the input and output data widths of multiples of 8-bit.

-

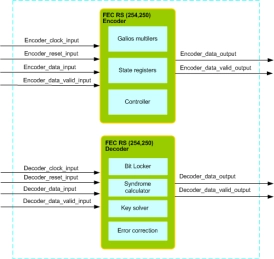

FEC RS (254,250) IIP

- VESA Display Port version 1.4/2.0/2.1 compliant.

- Supports full FEC functionality.

- Supports Reed Solomon (254,250) FEC, 10-bit symbols.

- Supports the input and output data widths of multiples of 10-bit.

-

FEC RS (198,194) IIP

- Supports the Universal Serial Bus 4 Specification and VESA Display Port version 2.0/2.1 Specification.

- Supports full FEC functionality.

- Supports Reed Solomon (198,194) FEC, 8-bit symbols.

- Supports the input and output data widths of multiples of 8-bit.

-

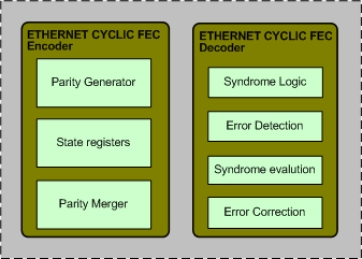

ETHERNET CYCLIC FEC IIP

- Compliant with ETHERNET specification.

- Supports Full IEEE Standard 802.3.2018 Ethernet cyclic FEC functionality.

- This FEC(Forward Error correction) methodology implements the (2112 , 2080) binary cyclic code is shortened from the cyclic Fire code (42987, 42955).

- Supports FEC of 32 bits parity bits.

-

Reed Solomon FEC

- Designed to support any Reed Solomon code.

- Custom tailored to support specific codes see standard table below

- Low Latency

- FEC Processing cycles optimized for reduced buffering