Denali IP

Filter

Compare

92

IP

from

2

vendors

(1

-

10)

-

Denali High-Speed DDR PHY for SMIC

- LPDDR4X/LPDDR4/LPDDR3/DDR4/DDR3/DDR3L training with write-leveling and data-eye training

- Optional clock gating available for low-power control

- Memory controller interface complies with DFI standards 4.0 or 3.1

- Internal and external datapath loopback modes

-

Denali High-Speed DDR PHY for TSMC 22ULP

- LPDDR4/LPDDR3/DDR4/DDR3/DDR3L training with write-leveling and data-eye training

- I/O pads with impedance calibration logic and data retention capability

- Optional clock gating available for low-power control

- Multiple PLLs for maximum system margin

-

Denali High-Speed DDR PHY for UMC

- LPDDR4/LPDDR3/DDR4/DDR3/DDR3L training with write-leveling and data-eye training

- I/O pads with impedance calibration logic and data retention capability

- Optional clock gating available for low-power control

- Multiple PLLs for maximum system margin

-

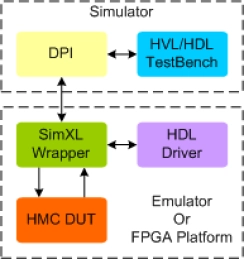

HMC Synthesizable Transactor

- Supports 100% of HMC protocol standard 1.0, 2.0 and 2.1

- Supports all the HMC commands as per the specs

- Supports 2,4 and 8 link configuration

- Supports for half width(8-lanes) and full width(16-lanes)

-

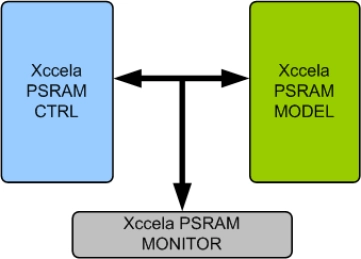

Xccela PSRAM Memory Model

- Supports Xccela PSRAM memory devices from all leading vendors

- Supports 100% of Xccela PSRAM protocol standard

- Supports all the Xccela PSRAM commands as per the specs

- Supports below Low Power Features

-

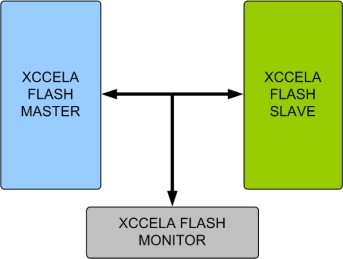

Xccela Flash Memory Model

- Supports Xccela Flash memory devices like MT35X_QLJW_U_256_ABA/ MT35X_QLKA_L_01G_BBA/ MT35X_QLKA_U_02G_CBA from all leading vendors

- Supports 100% of Xccela Flash protocol Standards.

- Supports all the Xccela Flash commands as per the specs.

- Supports Single and double transfer rate (SDR/DDR)

-

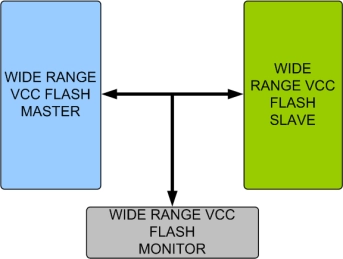

Wide Range VCC Flash Memory Model

- Supports Wide Range VCC Flash memory devices like MX25R3235F, MX25R1635F, MX25R6435 from all leading vendors

- Supports 100% of Wide Range VCC Flash protocol standards.

- Supports all the Wide Range VCC Flash commands as per the specs.

- Supports Serial Peripheral Interface - Mode 0 and Mode 3

-

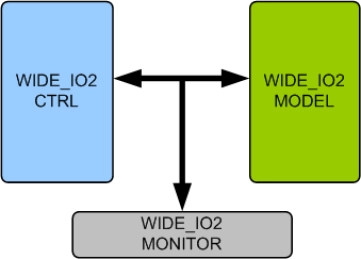

WIDE IO2 Memory Model

- Supports WIDE IO2 memory devices from all leading vendors.

- Supports 100% of WIDE IO2 protocol standard JESD229-2.

- Supports all the WIDE IO2 commands as per the specs.

- Quickly validates the implementation of the WIDE IO2 standard JESD229-2.

-

WIDE IO Memory Model

- Supports WIDE IO memory devices from all leading vendors.

- Supports 100% of WIDE IO protocol standard JESD229.

- Supports all the WIDE IO commands as per the specs.

- Quickly validates the implementation of the WIDE IO standard JESD229.