Clock Buffer IP

Filter

Compare

467

IP

from

103

vendors

(1

-

10)

-

Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS

- Max Load: 25pF total (including padcell and bondwire parasitics)

- Signal Integrity: Maintains tight rise/fall timing (1.4-3.1ns) across a wide load range (1pF to 26pF)

- Low Propagation Delay: 6ns typical delay at max load, ensuring fast response for real-time systems

- Efficient Power Use: 6.5mA average current at 40MHz with 25pF load, balancing performance and energy efficiency

-

SMIC 65nm LL Small signal digital clock buffer for baseband application

- Small signal digital clock buffer for baseband application;

- Cell Size (Width * height)90um * 180um with DUP stagger bonding pads;

- Work voltage: 1.2V power;

- Support >600mV clock signal input;Support 0.3V~0.5V wide input offset voltage range;

-

100MHz Reference Clock Single-end to Differential Buffer for PCIE Gen.I; UMC 0.13um HS/FSG LOGIC/MIXEDMODE Enhance Process

-

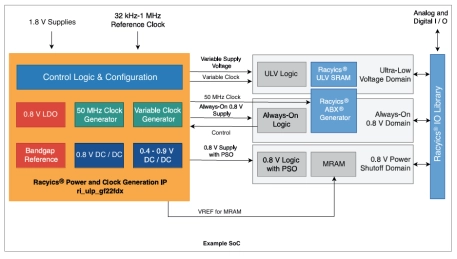

Power and Clock Generation IP - GLOBALFOUNDRIES® 22FDX®

- Tightly integrated power management platform with a soft-IP wrapper around Analog / Mixed-Signal hard macros which generate all supply voltages and clock signals needed to run highly efficient SoCs in GlobalFoundries® 22FDX®.

- Running from only one supply voltage and reference clock, the IP generates its own internal supplies and references, and those needed to run the Racyics® ABX® Generator.

-

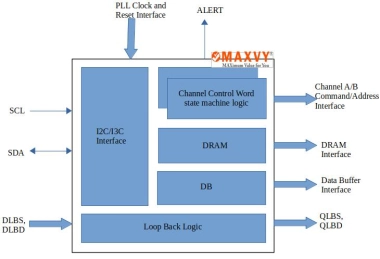

DDR5 REGISTERING CLOCK DRIVER (RCD) IP - (DDR5RCD03)

- The DDR5RCD03 is a registering clock driver used on DDR5 RDIMMs and LRDIMMs

- Its primary function is to buffer the Command/Address (CA) bus, chip selects, and clock between the host controller and the DRAMs

- It also creates a BCOM bus which controls the data buffers for LRDIMMs